#### **Object-Oriented Design Frameworks: Formal Specification and Some Implementation Issues**

#### Ivica Crnkovic

Department of Computer Engineering, Mälardalen University 721 23 Västerås, Sweden E-mail: Ivica.Crnkovic@mdh.se

#### Juliana Küster Filipe\*

Abt. Informationssysteme, Informatik, Technische Universität Braunschweig Postfach 3329, D-38023 Braunschweig, Germany E-mail: J.Kuester-Filipe@tu-bs.de

#### Magnus Larsson

ABB Automation Products AB, LAB 721 59 Västerås, Sweden E-mail: Magnus.Larsson@mdh.se

#### Kung-Kiu Lau

Department of Computer Science, University of Manchester Manchester M13 9PL, United Kingdom E-mail: kung-kiu@cs.man.ac.uk

#### Abstract

In component-based software development, object-oriented design (OOD) frameworks are increasingly recognised as better units of reuse than objects. This is because OOD frameworks are groups of interacting objects, and as such they can better reflect practical systems in which objects tend to have more than one role in more than one context. In this paper, we show how to formally specify OOD frameworks, and briefly discuss their implementation and configuration management.

Keywords: Object-oriented design frameworks, component-based software development.

#### 1. Introduction

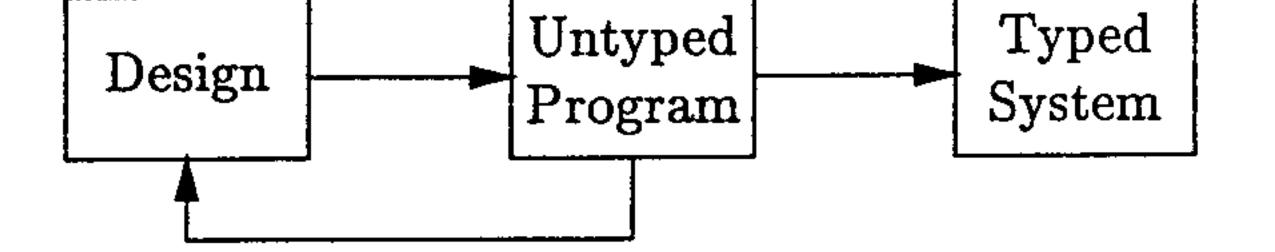

Object-Oriented Design (OOD) frameworks are groups of (interacting) objects. For example, in the CBD (Component-based Software Development) methodology *Catalysis* [10], a driver

| Driver |       |        |

|--------|-------|--------|

| Car    | rives | Person |

Figure 1. The Driver OOD framework.

may be represented as the OOD framework shown in Figure  $1.^1$  A driver is a person who drives a car, or in OOD terminology, a driver is a framework composed of a car object and a person object, linked by a 'drives' association (or attribute).

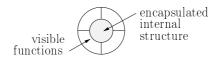

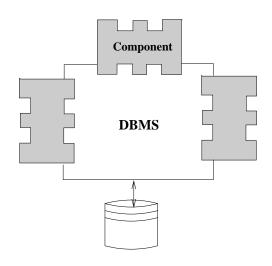

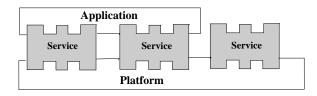

OOD frameworks are increasingly recognised as better units of reuse in software development than objects (see e.g. [12, 20]). The reason for this is that in practical systems, objects tend to have more than one role in more than one context, and OOD frameworks can capture this, whereas existing OOD methods (e.g. Fusion [6] and Syntropy [8]) cannot. The latter use classes or objects as the basic unit of design or reuse, and are based on the traditional view of an object, as shown in Figure 2, which regards an object as a closed entity with one fixed role. On the other hand, OOD frameworks allow objects that play different roles in different

Figure 2. Traditional view of an object.

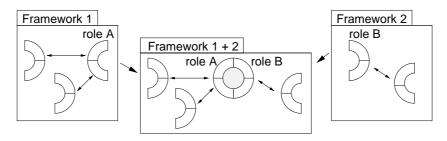

frameworks to be composed by composing OOD frameworks. In *Catalysis*, for instance, this is depicted in Figure 3.

Figure 3. Objects by composing OOD frameworks.

For example, a person can play the roles of a driver and of a guest at a motel simultaneously. These roles are shown separately in the PersonAsDriver and PersonAsGuest OOD frameworks in Figure 4. If we compose these two frameworks, then we get the PersonAsDriverGuest OOD framework as shown in Figure 5. In this OOD framework, a person object plays two roles, and is a composite object of the kind depicted in Figure 3.

OOD frameworks should play a crucial role in the design and implementation of nextgeneration component-based software systems. In this paper, we show how to formally specify them, and briefly discuss their implementation (in COM) and configuration management.

<sup>\*</sup>The second author was supported by the DFG under Eh75/11-2 and partially by the EU under ESPRIT-IV WG 22704 ASPIRE.

<sup>&</sup>lt;sup>1</sup>Catalysis uses the UML notation, see e.g. [21].

| PersonAsDriver    | PersonAsGuest      |

|-------------------|--------------------|

| Car drives Person | Person stays Motel |

Figure 4. PersonAsDriver and PersonAsGuest OOD frameworks.

| PersonAsDriver( | Guest  |         |       |

|-----------------|--------|---------|-------|

| Car             | Person | stays [ | Motel |

Figure 5. PersonAsDriverGuest OOD framework.

#### 2. Formal Specification of OOD Frameworks

In this section, we describe formal specification of OOD frameworks. First we consider the *static* aspects, i.e. *without* time or state transitions, then we consider the *dynamic* aspects, i.e. *with* time and state transitions.

#### 2.1. Static Aspects

We have considered the static aspects of OOD frameworks in [17, 18]. In this section, we briefly outline this semantics.

As we have seen in Section 1., OOD frameworks are composite objects/classes. In our approach, we define OOD frameworks and objects/classes in terms of a basic entity that we call a *specification framework*, or just a *framework*, for short.<sup>2</sup>

A framework  $\mathcal{F} = \langle \Sigma, X \rangle$  is defined in the context of first-order logic with identity. It is composed of a signature  $\Sigma$  (containing sort symbols, function declarations and relation declarations), and a finite or recursive set X of  $\Sigma$ -axioms. The purpose of a framework is to axiomatise a problem domain and to reason about it. In our approach, a problem domain contains the ADT's and classes needed to define the objects of the application at hand.

A framework is thus a (first-order) theory, and we choose its intended model to be a *reachable* isoinitial model, defined as follows:<sup>3</sup>

Let X be a set of  $\Sigma$ -axioms. A  $\Sigma$ -structure i is an *isoinitial model* of X iff, for every other model **m** of X, there is one isomorphic embedding  $i : i \to m$ .

A model i is *reachable* if its elements can be represented by ground terms.

We distinguish between *closed* and *open* frameworks. The relationship between open and closed frameworks plays a crucial role in our interpretation of objects. Roughly speaking, in object-oriented programming terminology, open frameworks represent *classes*, and closed frameworks represent their instances, i.e. *objects*.

A framework  $\mathcal{F} = \langle \Sigma, X \rangle$  is *closed* iff there is a reachable isoinitial model i of X.

An open framework  $\mathcal{F}(\Omega) = \langle \Sigma, X \rangle$  does not have an isoinitial model, since its axioms leave open the meaning of some symbols  $\Omega$  of the signature, that we call open symbols. Non-open symbols are called *defined* symbols.

Open frameworks can be *closed*, i.e made into closed frameworks, by instantiating its open symbols. We will use only open frameworks which have reachable isoinitial models for all their

$<sup>^2{\</sup>rm To}$  avoid confusion with OOD frameworks, in this section we will use 'framework' to refer to a specification framework only, and not to an OOD framework.

<sup>&</sup>lt;sup>3</sup>See [18] for a justification of this choice and [3, 16] for a discussion of isoinitial theories.

instances. Such frameworks are called *adequate*, and they can be constructed incrementally from small (adequate) closed frameworks (see [17, 18]).

**Example 2..1** The Car class in Figures 4 and 5 can be defined as the following *open* framework:

**OBJ-Framework** CAR(.km, .option);IMPORT: INT, year96; DECLS:  $.km : [] \rightarrow Int$  .option : [year96.opts]CONSTRS:  $.km \ge 0$

where  $\mathcal{INT}$  is a predefined ADT of integers, and *year*96 is an object that contains the sort *year*96.*opts* of the possible options for a car in the year 96. The constraint  $.km \ge 0$  is an axiom for the open symbol .km.

We call a framework like this an *OBJ-framework*, since it is a class of objects. To obtain objects we instantiate an OBJ-framework, i.e. by closing the OBJ-framework.

The axioms used to close  $\mathcal{F}(\Omega)$  into an object represent the *state* of the object, and are called *state axioms*. State axioms can be updated, i.e. an object is a dynamic entity.

An object of class  $\mathcal{CAR}$  is created, for example, by:

| NEW sp | $ider: \mathcal{CAR};$ |    |                                                                 |

|--------|------------------------|----|-----------------------------------------------------------------|

| CLOSE: | spider.km              | BY | spider.km = 25000;                                              |

|        | spider. option         | ΒY | $spider.option(x) \leftrightarrow x = Airbag \lor x = AirCond.$ |

where spider.km = 25000 and  $spider.option(x) \leftrightarrow x = Airbag \lor x = AirCond$  are (explicit) definitions that close the constant spider.km and the predicate spider.option(x) respectively.

The state of a spider object can be updated, by redefining its state axioms:

UPDATE spider : CAR; spider.km = 27000 spider.option(x)  $\leftrightarrow$  x = Airbag  $\lor$  x = AirCond

As we can see, the constant spider.km has been changed.

An OOD framework is a composite OBJ-framework. It can be viewed as a *system* of objects, in which objects can be created (and deleted) and updated dynamically.

**Example 2..2** The PersonAsDriver OOD framework in Figure 5 can be formalised as the following framework:

**OOD-Framework** DRIVER[PERSON, CAR];DECLS: .drives: [obj];CONSTRS:  $`X.drives(c) \rightarrow PERSON(`X) \land `X.age \ge 18 \land CAR(c);$  $(\exists c: obj)(.drives(c));$

where obj is a reserved sort symbol that contains the set of names of all existing objects in the system; 'X is a meta-symbol that stands for any object name; and the OBJ-framework  $\mathcal{PERSON}$  may be something like:

#### **OBJ-Framework** $\mathcal{PERSON}$ ;

IMPORT ...; DECLS: .name :  $\rightarrow$  string; .age :  $\rightarrow$  int;... CONSTRS: .age  $\geq 0$

Here the composite object is built via links between its components, which constrain object creation (and deletion) methods. We cannot create an object n.DRIVER, if n is not a person. Furthermore, we need at least one car c.

#### 2.2. Dynamic Aspects

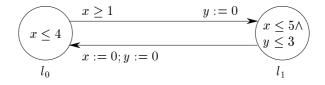

In this section, we consider how to introduce time and state changes. We will combine the static formalisation outlined in the previous section with the logic MDTL presented in [13]. MDTL is an extension of the TROLL logic [11] for describing dynamic aspects of large object systems.

#### 2.2.1. State Transitions.

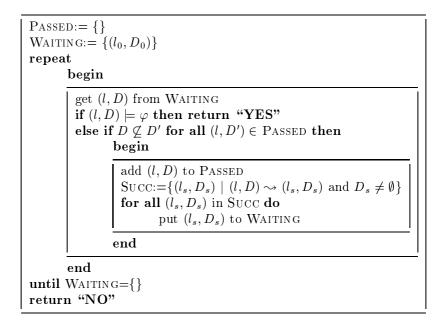

In MDTL, an OBJ or OOD framework has a local logic consisting of a *home* and a *communication* logic. The *home* logic allows us to express internal state changes, whereas the *communication* logic describes framework interactions. The *home* logic of a framework is mainly a first-order temporal logic with (true) concurrency. We do not deal with concurrency explicitly in this paper, and so we will use axioms that are just first-order temporal formulae. Also, in this paper, we will not use the communication logic, since we do not deal with framework interactions.

In MDTL, in addition to attributes, an object also has *actions*,<sup>4</sup> which will affect its current state. Actions may be either *enabled* or *occurring* in a particular state. The *state* of an object is given by the current values of the attributes, and the current status of its actions. Thus in MDTL, a state formula is a conjunction of facts (the current values of the attributes) and actions (enabled or occurring).

If an action is *enabled*, then it may occur in the next state. When an action occurs, the state of the object changes. In the logic,  $\odot a$  is used to denote the occurrence of action a, and  $\triangleright a$  that the action a is enabled. If an action occurs, then it must have been enabled in the previous state:  $\odot a \Rightarrow Y \triangleright a$ . In this formula, Y is the temporal operator Yesterday referring to the previous state. Enabling ( $\triangleright$ ) is useful for expressing *preconditions*, and occurrence ( $\odot$ ) for expressing *postconditions*.

In the sequel, we shall also use the temporal operators X (next state), F (sometime in the future including the present), and P (sometime in the past including the present).

The state of an OOD framework is given by the states of the current objects belonging to the framework.

We illustrate how to specify state transitions of an OOD framework in MDTL with a simple example.

**Example 2..3** Consider the OOD framework for employees as depicted in Figure 6, in which a person plays the role of an employee of a company. A person as an employee has an attribute *pocket* representing the amount of money he possesses, and two actions *receive\_pay* and *work*.

<sup>&</sup>lt;sup>4</sup>More commonly known as *methods* in object-oriented programming.

| PersonAsEmployee |                                                                                    |

|------------------|------------------------------------------------------------------------------------|

| Company worksfor | Person<br>pocket: Money                                                            |

|                  | receive_pay(amt: Money)<br>pre: has worked before<br>post: pocket increased by amt |

|                  | work()<br>pre: pocket<500                                                          |

Figure 6. PersonAsEmployee OOD framework.

In this example, a person as an employee only works if he has less than  $\pounds 500$  (precondition for work). A person only receives a payment if he has worked before (precondition for  $receive\_pay$ ). If a person receives a payment, the money in his pocket increases by the amount received. Here, we express the pre- and postconditions only informally, and we omit the parameters and the postcondition of work, as well as the definition of the OBJ-framework for Company.

The class Person might be formalised by the following OBJ-framework:

```

OBJ-Framework \mathcal{PERSON};

```

where the ST-AXIOMS are the state transition axioms.

Pre- and postconditions allow us to define the state transitions of a framework. The state transition axioms do not affect the (static) isoinitial model of the OBJ-framework, and are relevant only for the behaviour model. The first axiom states that if the action receive\_pay is enabled, then sometime in the past (temporal operator P) the action work(...) must have occurred. The second axiom says that the occurrence of action  $receive\_pay(a)$  implies that if in the previous state the value of pocket was n, then its current value is n + a. Finally, the third axiom states that if the action work(...) is enabled (it might occur in the next state) then the value of pocket must be less than  $\pounds$  500.

We can create an object *joe* of Person class as follows:

NEW joe :  $\mathcal{PERSON}$ ; CLOSE: joe.pocket BY joe.pocket = £100; joe.work BY  $\triangleright$  joe.work(...); joe.pay BY  $\neg \triangleright$  joe.receive\_pay(a).

When an object is created, its initial state is defined. In the initial state of *joe*, (attribute) pocket is £100, (action) receive\_pay(a) is disabled for any a, and (action) work(...) enabled.

In MDTL we can also express general properties of objects. For example,<sup>5</sup>

$$joe.pocket < \pounds 500 \Rightarrow F \exists_a \odot joe.receive\_pay(a)$$

means 'if *joe* has less than  $\pounds 500$  then he will receive a payment sometime'.

#### 2.2.2. Event Structures.

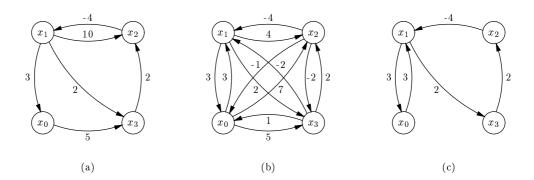

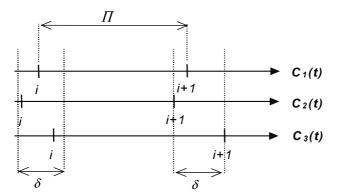

MDTL is interpreted over *labelled prime event structures* ([24]). A labelled prime event structure is thus a model for an OOD framework if it satisfies all the axioms of the framework (both the static and the state transition axioms).

A labelled prime event structure consists of a prime event structure and a labelling function. Prime event structures can be used to describe distributed computations as event occurrences together with a *causal* and a *conflict* relations between them. The causal relation implies a (partial) order among event occurrences, and the conflict relation denotes a choice. Events in conflict cannot belong to the same *run* or *life cycle*. The labelling function associates each event with a state.

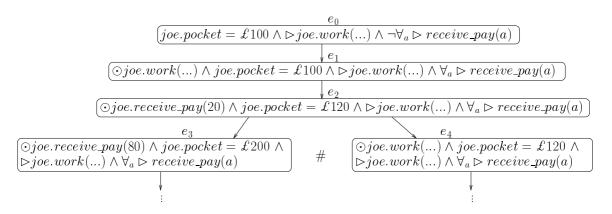

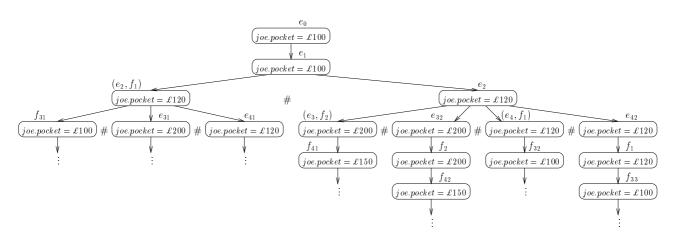

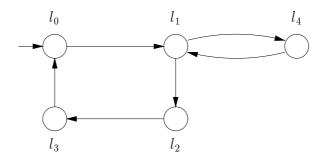

**Example 2..4** Consider the event structure in Figure 7. It shows a small part of a (sequential)

Figure 7. Event structure for *joe* as an employee.

behaviour model for *joe*.

In general, in event structures, *boxes* denote events  $\{e_0, e_1, \ldots\}$ , *arrows* between boxes represent event *causality*, and # denotes event *conflict*. The state of the object at a given event is written inside the box as a state formula.

For the object *joe*, the events in the event structure are labelled by the formulae of the state logic of the Person class. Event  $e_0$  corresponds to the initial state. The occurrence of  $e_1$  depends on the previous occurrence of  $e_0$ . With the occurrence of action *joe.receive\_pay*(20) at event  $e_2$ , the current value of attribute *pocket* changes to £120. Events  $e_3$  and  $e_4$  are in conflict, which means that either one or the other occurs but not both. A conflict thus denotes a choice.

There are therefore two life cycles for *joe* in Figure 7. One consists of events  $\{e_0, e_1, e_2, e_3, \ldots\}$  and the other  $\{e_0, e_1, e_2, e_4, \ldots\}$ . In the former, *joe* receives two payments after working. In the latter, *joe* works, then receives a payment and then works again.

Finally, it is easy to see that this event structure satisfies the state transition axioms of the OBJ-framework  $\mathcal{PERSON}$ .

<sup>&</sup>lt;sup>5</sup>We are not saying that this property necessarily follows from the ST-axioms of the object *joe*.

In general, labelled event structures provide models for concurrent computations. Other such models include transition systems, Petri nets, traces, and synchronisation trees. Petri nets and transition systems allow an explicit representation of the (possibly repeating) states in a system, whereas trees, traces and event structures abstract away from such information, and focus instead on the behaviour in terms of patterns of occurrences of actions over time. Furthermore, event structures are a "true" concurrency model, as opposed to transition systems that model systems as non-deterministically interleaved sequential computations. A detailed survey and comparison of some of these models can be found in [24].

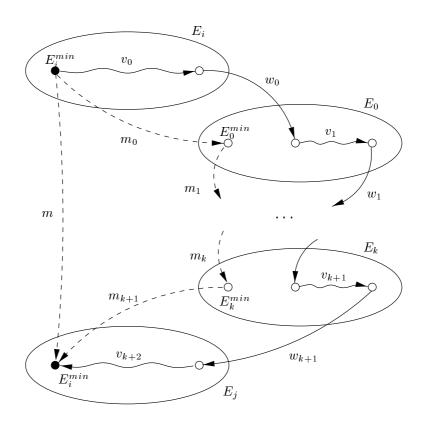

#### 2.2.3. Composing Event Structures.

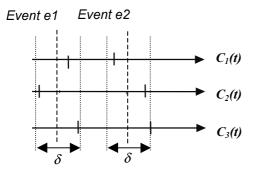

In order to create objects by composing OOD frameworks with state transitions in the manner depicted in Figure 3, we need to be able to compose event structures.

**Example 2..5** In the previous example, a person plays the role of an employee. This partial definition of person could be combined with another view of a person, e.g., a person as a consumer. The PersonAsConsumer OOD framework in Figure 8 defines this role for a person

| PersonAsConsumer                                                                       |               |

|----------------------------------------------------------------------------------------|---------------|

| Person<br>pocket: Money                                                                | buysfrom Shop |

| buy(price: Money)<br>pre: price <pocket<br>post: pocket decreased by price</pocket<br> |               |

Figure 8. PersonAsConsumer OOD framework.

object. The class Person here can be defined by the same OBJ-framework  $\mathcal{PERSON}$  in Example 2..3, but with the action buy(p) instead of the actions  $receive\_pay(a)$  and  $work(\ldots)$ . We omit the definition of the OBJ-framework for Shop.

A consumer has an action buy(p), where p represents the price of the item bought. Preand postconditions for this action are the expected ones. A consumer may only buy something if he has enough money, and after buying an item the money in his pocket decreases by the amount of money spent. The state transition axioms for buy(p) are thus:

$$\begin{array}{l} \forall_p \rhd .buy(p) \Rightarrow .pocket > p \\ \forall_{p,n} \odot .buy(p) \Rightarrow Y(.pocket = n) \Rightarrow .pocket = n - p \end{array}$$

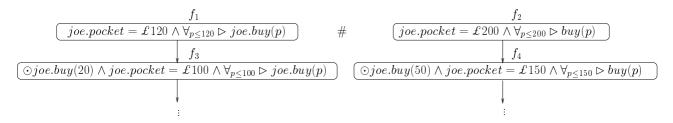

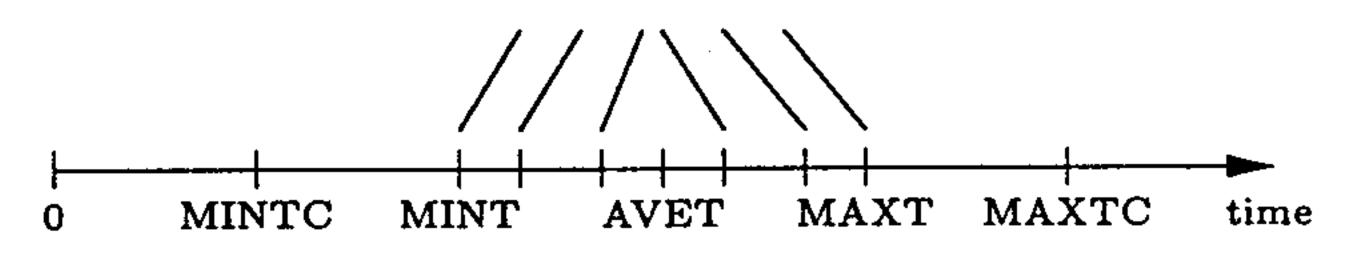

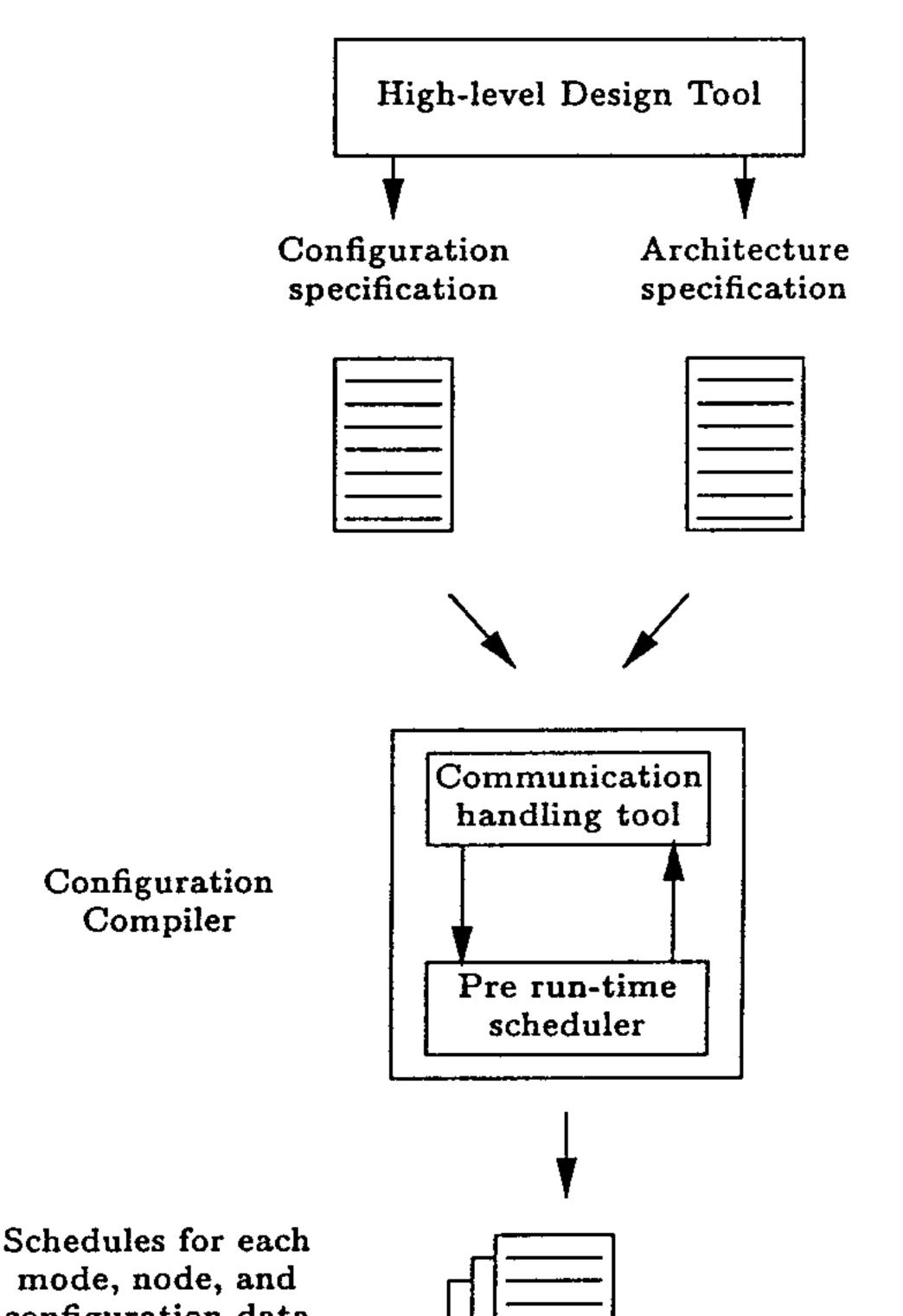

Let *joe* be a person playing now the role of a consumer. In the event structure for *joe* as a consumer, a life cycle is a linear sequence of *buy* events starting from the initial state in which *joe.pocket* is initialised. In Figure 9, we show two possible life cycles with distinct initial states.

We may compose the OOD frameworks for PersonAsEmployee and PersonAsConsumer, to obtain a person with both roles together. A person now has all the actions of both roles, namely *receive\_pay*, *work* and *buy*, and the attribute *pocket* in both roles. The composition is illustrated by Figure 10.

The composite PersonAsEmployeeConsumer framework contains the union of the state transition axioms of its component OOD frameworks. An event structure, i.e. a model, for a person as an employee and consumer is obtained by composing a model for person as an employee with one for person as a consumer in a special manner. Several constructions for sequential and parallel composition of event structures have been defined in the literature, e.g. [23, 19]. What we

Figure 9. Event structure for *joe* as a consumer.

| PersonAsEmployee | Consumer                                                    |               |

|------------------|-------------------------------------------------------------|---------------|

| Company          | Person<br>pocket: Money<br>receive_pay(amt:Money)<br>work() | buysfrom Shop |

|                  | buy(price:Money)                                            |               |

Figure 10. PersonAsEmployeeConsumer OOD framework.

need for composing roles is in fact a combination of *interleaving* of the models and *synchronisation*. Interleaving (sequential composition), because we are combining models for the same object in different roles (and objects are considered to behave sequentially), and therefore the composed model must be sequential. Synchronisation, because some attributes and/or actions for distinct roles may be identified as the same (e.g. *pocket*).

Figure 11 shows the composed model for *joe* as an employee and consumer based on the models of Figures 7 and 9 for *joe* as an employee and *joe* as a consumer respectively. In this

Figure 11. Event structure for *joe* as an employee and a consumer.

case, event synchronisation is done over the value of the common attribute *pocket*. That is, only those events of both models that have the same value for pocket may be synchronised, e.g., events  $e_2$  and  $f_1$ ,  $e_3$  and  $f_2$ , and  $e_4$  and  $f_1$ . Synchronisation is indicated by the pairs  $(e_2, f_1)$ , etc.

Normally, synchronisation is done over actions, but we have a new situation here by combining roles, namely that the attribute *pocket* of a person as an employee is to be identified with the attribute *pocket* of a person as a consumer, whereas the actions *receive\_pay*, *work* and *buy* are all distinct. Synchronisation is not always necessary, and some of the life cycles in Figure 11 show just interleaving.

The construction of composite event structures sometimes leads to the duplication of events, e.g., event  $e_3$  has been duplicated and corresponds to events  $e_{31}$  and  $e_{32}$ . The labels of these events are the same as  $e_3$ . In Figure 11, the states are just indicated by the value of the attribute *pocket* for simplicity. The label of event  $(e_2, f_1)$  is given by the conjunction of the labels  $e_2$  and  $f_1$ , i.e., it corresponds to the formula

$$\begin{array}{l} joe.pocket = \pounds 120 \land \odot receive\_pay(20) \land \rhd joe.work \land \forall_a receive\_pay(a) \land \forall_{p \leq 120} \rhd buy(p) \end{array}$$

Parallel composition of event structures with synchronisation is useful for modelling interacting frameworks (e.g., [15]), whereas without synchronisation it models non-interacting frameworks.

#### 3. Some Implementation Issues

Having shown how to formally specify OOD frameworks, we now turn to practical concerns. In particular, we will discuss how we might construct such frameworks in practice using currently available technology, and the issues involved in such constructions.

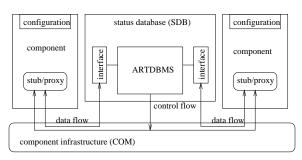

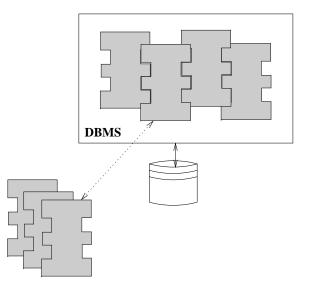

Of the current technologies for developing component-based software systems, COM [5] seems to lend itself most readily to the implementation of OOD frameworks. Therefore, we will briefly show how to implement OOD frameworks in COM.

The fact that OOD frameworks are composite objects/classes means that constructing these frameworks creates problems for *configuration management*. Therefore, we will consider some of these problems, in the case of COM implementations.

#### 3.1. Implementing OOD Frameworks in COM

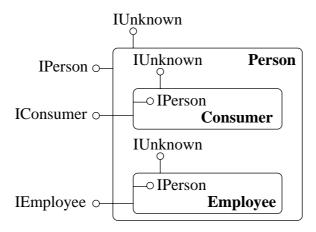

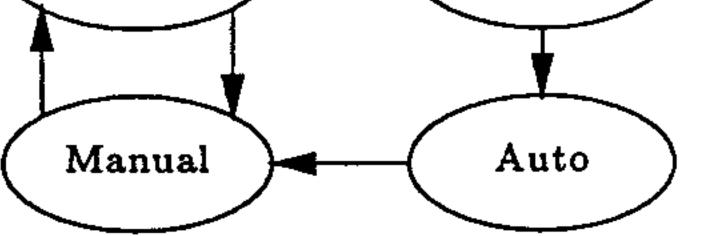

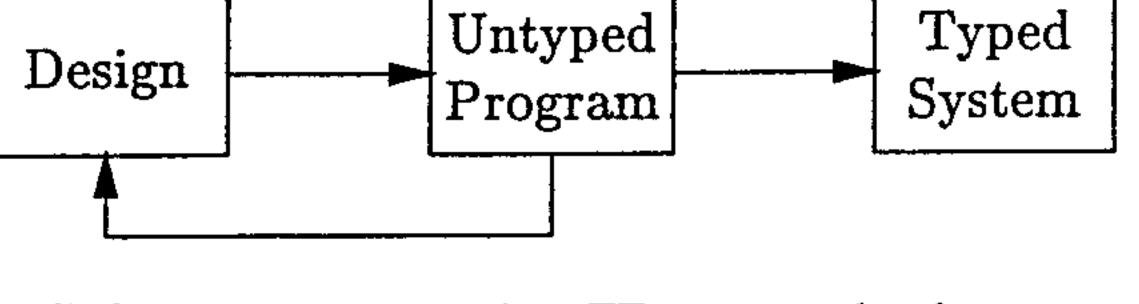

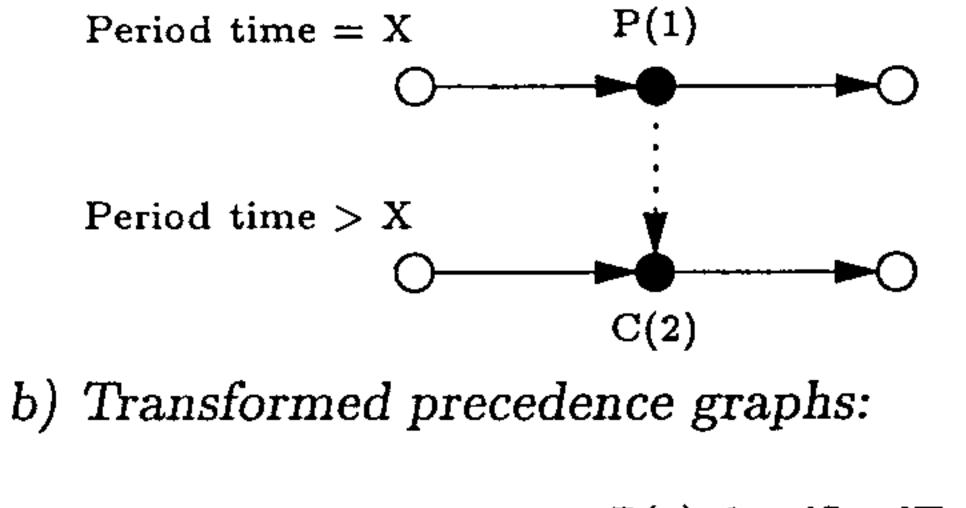

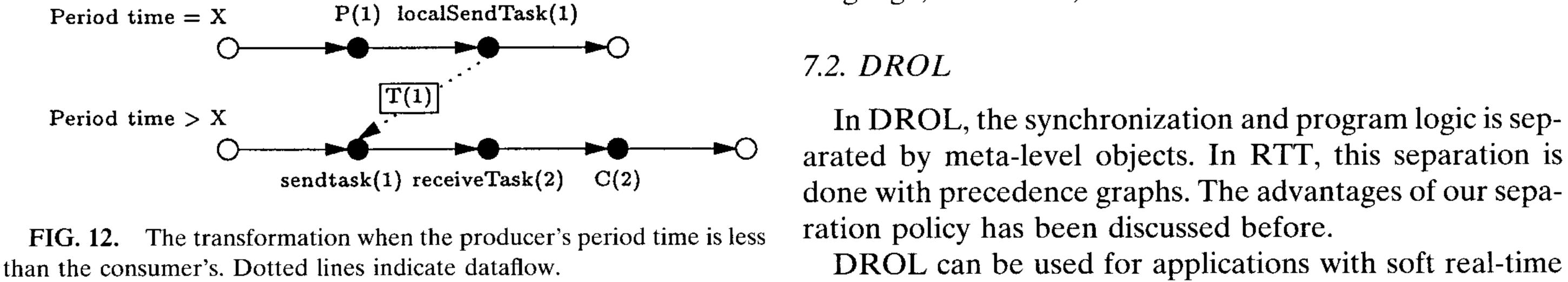

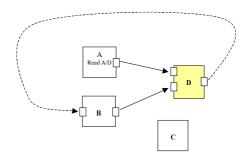

In this section, we show how to use COM to implement the OOD frameworks in Figures 6, 8 and 10. COM suits multiple roles because it can use multiple interfaces for each role. We will use the aggregation mechanism in COM to compose OOD frameworks. First, we implement the Person object, which corresponds to the encapsulated internal structure in Figure 2. The Person object is constructed so it supports aggregation of role objects and it has one IPerson interface (see Figure 12).

Figure 12. A COM object for the person object and the consumer role.

Secondly, the consumer and employee roles are implemented so they support being aggregated into a person object. Figure 12 shows the consumer role with one IConsumer interface. The consumer object also needs a reference to the person object to be able to work on the pocket variable. The person reference is set up when the consumer is aggregated into the person object (see Figure 13). In a similar way the employee role is implemented. Using aggregation we can reuse the different components that we have created. Figure 13 shows how Person aggregates the two already defined COM objects. Frameworks are created at run-time by adding roles to an object.

Figure 13. The Consumer and Employee roles are aggregated into the Person object.

The COM implementation of the framework concept has some limitations. The COM model defines frameworks as aggregates of the completed objects created at run-time, while a general framework model allows us to use incomplete objects (at run-time) or classes (at build-time).

#### 3.2. Configuration Management

Using OOD frameworks instead of traditional objects yields several advantages, but it also introduces an additional level of complexity when building these frameworks. Frameworks are composite types of entities – they have an internal structure which is built from objects, or from parts of them. A framework entity also has relations to other frameworks, and can be composed from other (sub)frameworks. The definition and creation of such a composite entity introduces configuration problems. Some of them will be illustrated here for a COM implementation.

Let us consider the following cases:

- Sharing objects in several frameworks;

- Composing frameworks from objects and frameworks.

#### 3.2.1. Sharing Objects in Several Frameworks.

Suppose framework  $F_1$  includes objects  $O_1$  and  $O_2$  with a relation  $R_{12}$  between them, and framework  $F_2$  contains objects  $O_1$  and  $O_3$  with a relation  $R_{13}$ . The object  $O_1$  is shared by two frameworks:

$$F_1 = \{O_1 O_2 ; R_{12}\}, \quad F_2 = \{O_1 O_3 ; R_{13}\}$$

(1)

Suppose we now add a new property to the object  $O_1$ , a property that is required in (an improved version of) framework  $F_2$ . This creates a new version of the object  $O_{1;v2}$ , (v2 denotes the new version) which is included into the framework  $F_2$ :

$$F_2 = \{ O_{1;v2} \ O_3 \ ; \ R_{13} \}$$

However, if we do not take versioning into consideration, then the framework specifications will remain the same. In this case, we can be aware of the change of the object  $O_1$  in the context of framework  $F_2$ , but not necessarily in that of  $F_1$ . Our specification of  $F_1$  is defined by (1), but in reality we have

$$F_1 = \{O_{1;v2} \ O_2 \ ; \ R_{12}\}$$

If the role of the object  $O_{1,v^2}$  used in  $F_1$  is changed, then the behaviour of  $F_1$  will be changed unpredictably, and a system using  $F_1$  can fail. To avoid these unpredictable situations we can introduce basic configuration management methods – a version management of objects and configuration of frameworks [7]:

- An object is identified by its name and version.

- A framework is identified by a name and a version. A new framework version is derived from object versions included in the framework.

These rules imply that new versions of frameworks will be configured when a new object version is created, as shown in our example:

$$F_{1;vi} = \{O_{1;vm} \ O_{2;vn} \ ; \ R_{12}\}, \quad F_{2;vk} = \{O_{1;vm} \ O_{3;vk} \ ; \ R_{13}\}$$

$$F_{1;vi+1} = \{O_{1;vm+1} \ O_{2;vn} \ ; \ R_{12}\}, \quad F_{2;vk+1} = \{O_{1;vm+1} \ O_{3;vk} \ ; \ R_{13}\}$$

As several frameworks can share one object, and a framework can contain several objects, the number of generated frameworks can grow explosively. It is, however, possible to limit the number of interesting configurations. Typically, in a development process, we would implement the changes on all the objects we want, collect the versions of objects we want in a baseline and derive the frameworks from the baselined object versions. In such a case, experience for similar cases [2] shows that the number of derived entities does not necessarily grow rapidly.

A shared object is not necessarily completely shared, but different parts of the object, defined by the object's roles, are used in the frameworks. In the COM implementation a complete object will be included, but a part of it will be used. In a general framework model, a class (or an object at run-time) includes only those parts which are specified in the object's role. When we define a new role for an object in a framework or re-define the existing one, we need to change a specific part of the object class. We call this specific part an object aspect. The change of an object aspect will affect only those frameworks where the aspect is included. Other frameworks, though containing the object (or part of it), are not affected by the change. In this case, it is better to keep version control on the aspect level, and relate a framework configuration to the object aspects.

If we declare an aspect as a subset of an object  $A_i(O_k) \subseteq O_k$ , then an object version is defined as a set of aspect versions:

$$O_{i;vk} = \{A_{j;vl}\}$$

and a framework version is defined as a set of aspect versions with relations between the aspects:

$$F_{vk} = \{\{A_{j;vl}(O_{i;vk})\}; R_{jl}\}$$

Having control over changes on the aspect level, we can gain control over the changes on the framework level. Now we can more precisely identify the frameworks being affected by changes in object roles.

#### 3.2.2. Composing Frameworks from Objects and Frameworks.

In the framework model it is possible to compose new frameworks from existing frameworks. A new framework is a superset of the classes and relations from the frameworks involved. If a new framework is created at run-time, as in a COM implementation, then the objects from the selected frameworks comprise the new framework. The following example illustrates the merging process of two frameworks  $F_1$  and  $F_2$  into  $F_3$ :

$$F_1 = \{O_1 O_2 ; R_{12}\}, F_2 = \{O_1 O_3 ; R_{13}\}, F_3 = \{O_1 O_2 O_3 ; R_{12}, R_{13}, R_{23}\}$$

The composition works fine as long as we do not need to consider the changes of objects within one framework.

Suppose we create a new object version (or a new object aspect version) in  $F_2$  and keep the old version of the same object in  $F_1$ :

$$F_{1;vi} = \{ O_{1;v1} \ O_{2;vk} \ ; \ R_{12} \}, \ F_{2;vj} = \{ O_{1;v1+1} \ O_{3;vl} \ ; \ R_{13} \}$$

In the merging process we have to recognise if different versions of the same objects are included in the frameworks being merged. If that is the case, we have two possible solutions:

• Selecting one specific version of the object (for example the latest):

$$F_{3;v1} = \{O_{1;v1+1} \ O_{2;vk} \ O_{3;v1} \ ; \ R_{12}, R_{13}, R_{23}\}$$

• Selecting both versions and enable their consistence in the new framework:

$$F_{3;v1} = \{ O_{1;v1} \ O_{1;v1+1} \ O_{2}; vk \ O_{3;v1} \ ; \ R_{12}, R_{13}, R_{23} \}$$

For the second case there must be support for identifying object versions. This support can be provided by introducing an identification interface [14] as the standard interface of an object. There must also be support for managing different versions of the same object in the running system.

#### 4. Conclusion

In this paper we have shown how to formally specify OOD frameworks using MDTL and event structures. In particular, we have shown a semantics for composing OOD frameworks with state transitions in the manner depicted in Figure 3.

Our work here is closely related to TROLL [11], which is used for specifying large distributed/concurrent object systems, and to [4], which formalises an algebraic semantics for object model diagrams in OMT [22]. The main difference is that they take the traditional view of objects (Figure 2), whereas we adopt the multiple-role, more reusable approach (Figure 3). Their semantics is based on initial theories, as opposed to isoinitial theories that we use.

Overall, our approach to specification is model-theoretic, whereas other approaches are mostly proof- or type-theoretic. For example, our model-theoretic characterisation of states and objects stands in contrast to the type-theoretic approach, e.g., [1]. Our model-theoretic approach also enables us to define a notion of correctness that is preserved through inheritance hierarchies, which is particularly suitable for component-based software development. We have also presented a possible implementation of OOD frameworks using the COM technology. This implementation has some limitations, and we need to do further work to investigate how to improve this implementation.

Finally we have discussed configuration management for frameworks. We emphasise a need for using configuration management methods for managing frameworks as composite objects. The configuration management issues are complicated and need further investigation: Questions of managing relations, concurrent versions of frameworks, inclusion of change management [9], etc., must be addressed. Since aspects and objects are not entities recognised by standard configuration management tools (which recognise entities such as files, directories, etc.), new, semantic-based rules must be incorporated into such tools. For different object-oriented and component technologies, different tools have to be made. How different do they need to be, and are there possibilities to define common rules and implementation? These are questions for future investigation.

#### Acknowledgements

We would like to thank the referee who pointed out some minor mistakes.

#### References

- [1] M. Abadi and L. Cardelli (1996). A Theory of Objects. Springer-Verlag.

- [2] U. Asklund, L. Bendix, H.B. Cristensen, and B. Magnusson (1999). The unified extensional versioning model. In J. Estublier, editor, Proc. System Configuration Management SCM-9, pages 17–33, Springer.

- [3] A. Bertoni, G. Mauri, and P. Miglioli (1983). On the power of model theory in specifying abstract data types and in capturing their recursiveness. *Fundamenta Informaticae* VI(2):127–170.

- [4] R.H. Bourdeau and B.H.C. Cheng (1995). A formal semantics for object model diagrams. IEEE Trans. Soft. Eng., 21(10):799-821.

- [5] D. Box (1998). Essential COM. Addison-Wesely.

- [6] D. Coleman, P. Arnold, S. Bodoff, C. Dollin, H. Gilchrist, F. Hayes, and P. Jeremaes (1994). *Object-Oriented Development: The Fusion Method*. Prentice-Hall.

- [7] R. Conradi and B. Westfechtel (1998). Version models for software configuration management. ACM Computing Surveys, 30(2):232-282.

- [8] S. Cook and J. Daniels (1994). Designing Object Systems. Prentice-Hall.

- [9] I. Crnkovic (1997). Experience with change oriented SCM Tools. In R. Conradi, editor, Proc. Software Configuration Management SCM-7, pages 222–234, Springer.

- [10] D.F. D'Souza and A.C. Wills (1998). Objects, Components, and Frameworks with UML: The Catalysis Approach. Addison-Wesley.

- [11] A. Grau, J. Küster Filipe, M. Kowsari, S. Eckstein, R. Pinger and H.-D. Ehrich (1998). The TROLL approach to conceptual modelling: syntax, semantics and tools. In T.W. Ling, S. Ram and M.L. Leebook, editors, *Proc. 17th Int. Conference on Conceptual Modeling*, *LNCS* 1507:277-290, Springer.

- [12] R. Helm, I.M. Holland, and D. Gangopadhay (1990). Contracts Specifying behavioural compositions in OO systems. Sigplan Notices 25(10) (Proc. ECOOP/OOPSLA 90).

- [13] J. Küster Filipe (2000). Fundamentals of a module logic for distributed object systems. J. Functional and Logic Programming 2000(3).

- [14] M. Larsson and I. Crnkovic (1999). New challenges for configuration management. In J. Estublier, editor, Proc. System Configuration Management SCM-9, pages 232–243, Springer.

- K.-K. Lau, S. Liu, M. Ornaghi, and A. Wills (1998). Interacting frameworks in *Catalysis*. In J. Staples, M. Hinchey and S. Liu, editors, *Proc. Second IEEE Int. Conf. on Formal Engineering Methods*, pages 110-119, IEEE Computer Society Press.

- [16] K.-K. Lau and M. Ornaghi (1998). Isoinitial models for logic programs: A preliminary study. In J.L. Freire-Nistal, M. Falaschi, and M. Vilares-Ferro, editors, *Proceedings of the* 1998 Joint Conference on Declarative Programming, pages 443-455, A Coruña, Spain.

- [17] K.-K. Lau and M. Ornaghi (1998). On specification and correctness of OOD frameworks in computational logic. In A. Brogi and P. Hill, editors, Proc. 1st Int. Workshop on Component-based Software Development in Computational Logic, pages 59-75, September 1998, Pisa, Italy.

- [18] K.-K. Lau and M. Ornaghi (1998). OOD frameworks in component-based software development in computational logic. In P. Flener, editor, Proc. LOPSTR'98, LNCS 1559:101-123, Springer-Verlag.

- [19] R. Loogen and U. Goltz (1991). Modelling nondeterministic concurrent processes with event structures. *Fundamenta Informaticae* **XIV**(1):39–73.

- [20] R. Mauth (1996). A better foundation: development frameworks let you build an application with reusable objects. BYTE 21(9):40IS 10-13.

- [21] R. Pooley and P. Stevens (1999). Using UML: Software Engineering with Objects and Components. Addison-Wesley.

- [22] J. Rumbaugh, M. Blaha, W. Premerlani, F. Eddy, and W. Sorenson (1991). Object-Oriented Modeling and Design. Prentice-Hall.

- [23] F.W. Vaandrager (1989). A simple definition for parallel composition of prime event structures. Technical Report CS-R8903, Centre for Mathematics and Computer Science, P.O. Box 4079, 1009 AB Amsterdam, The Netherlands.

- [24] G. Winskel and M. Nielsen (1995). Models for concurrency. In S. Abramsky, D.M. Gabbay, and T.S.E. Maibaum, editors, *Handbook of Logic in Computer Science*, Vol. 4, Semantic Modelling, pages 1–148. Oxford Science Publications.

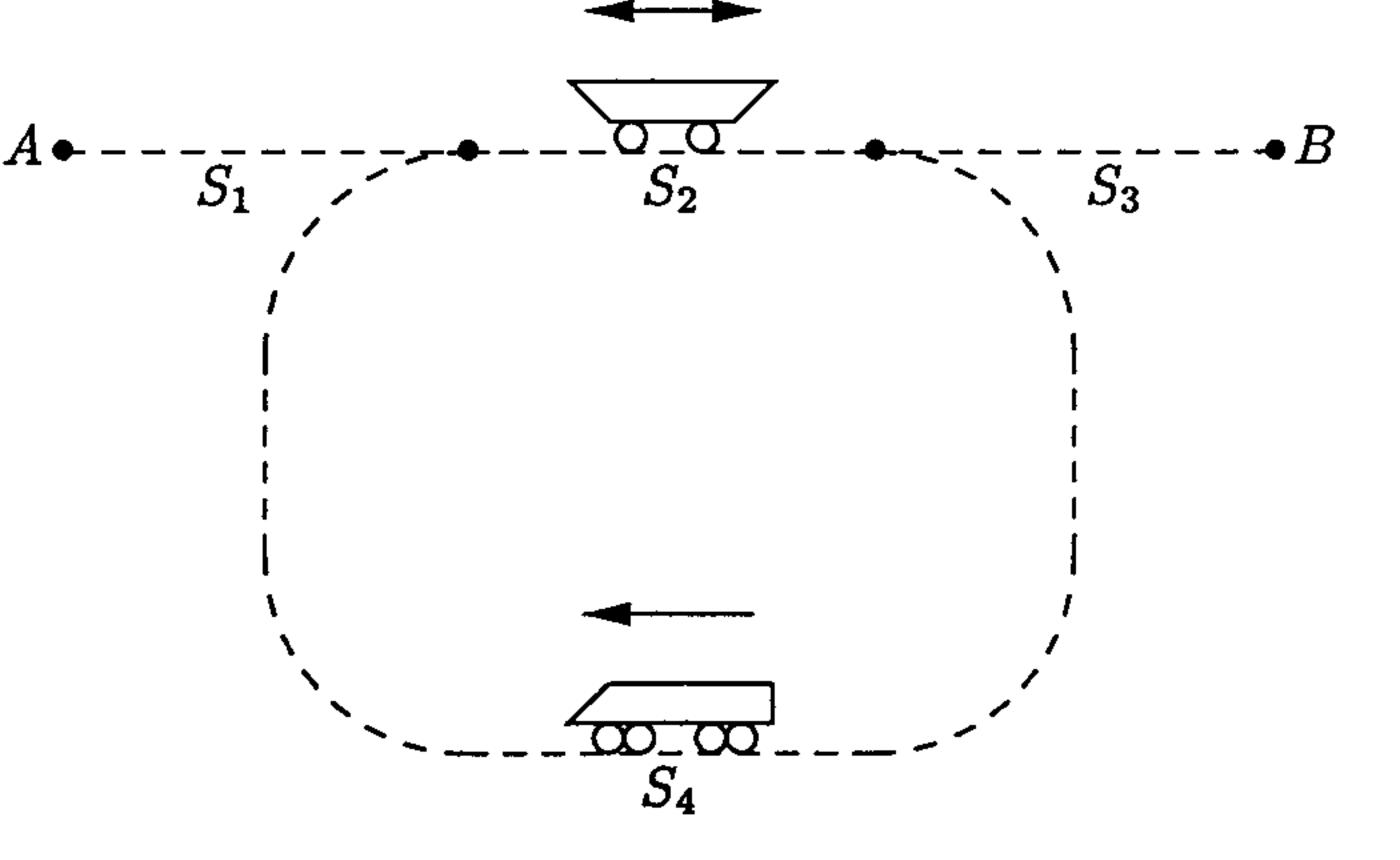

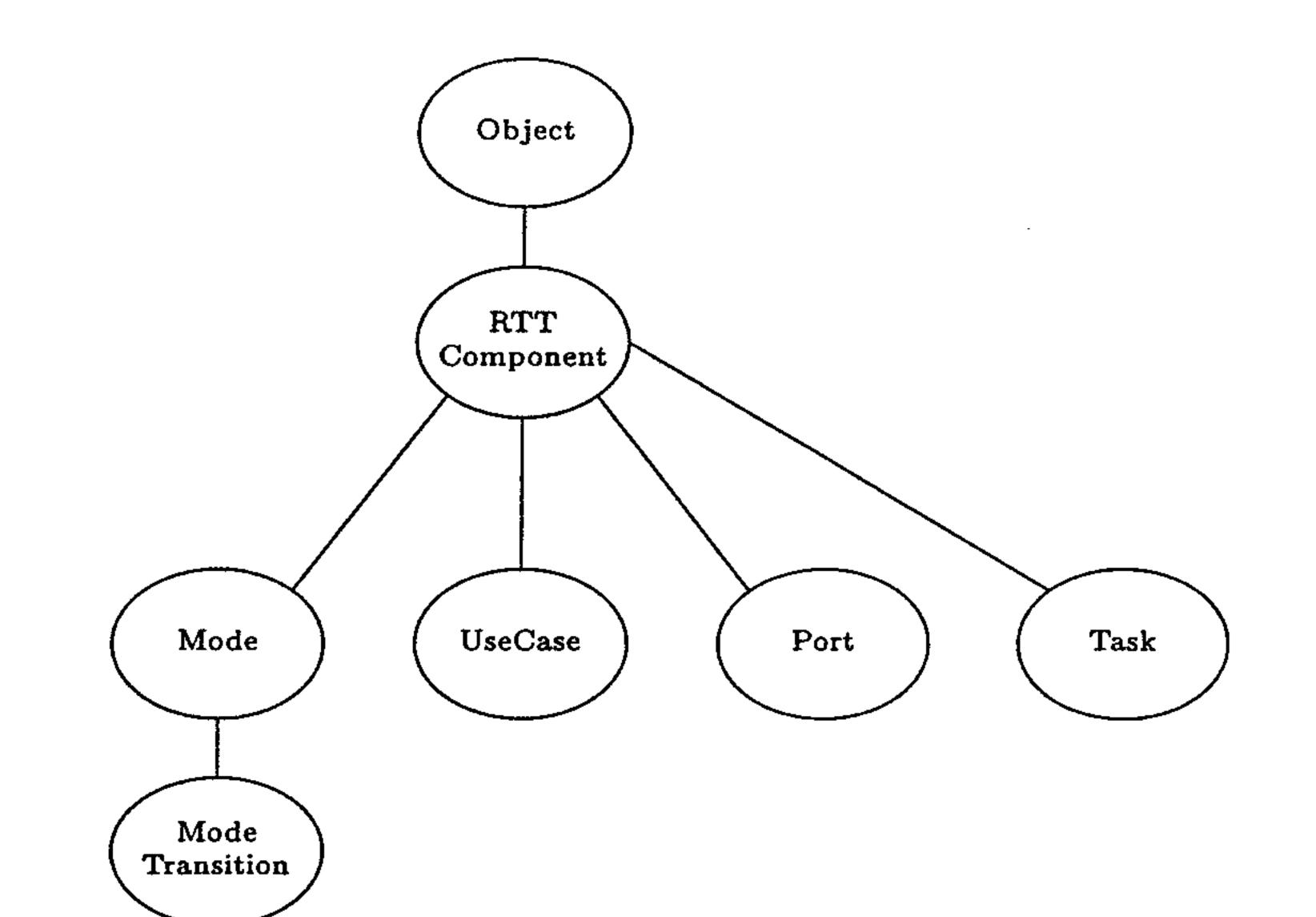

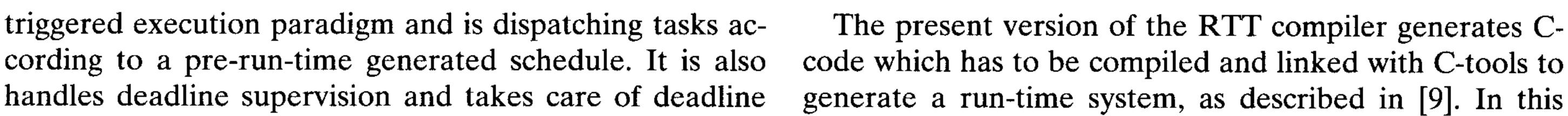

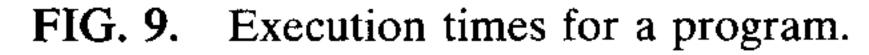

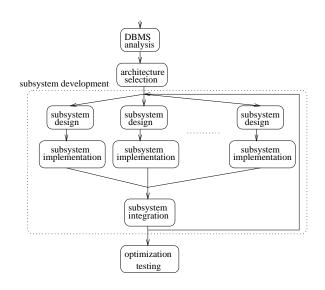

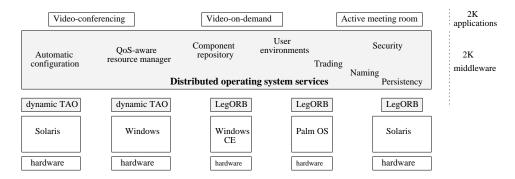

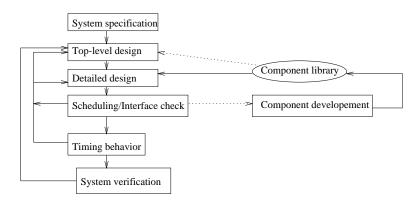

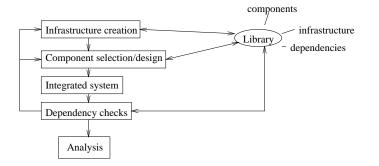

#### Towards a Toolset for Architectural Design of Distributed Real-Time Control Systems

Jad El-khoury and Martin Törngren The Mechatronics Lab, Department of Machine Design Royal Institute of Technology - KTH, Stockholm, Sweden {jad, martin}@md.kth.se

#### Abstract

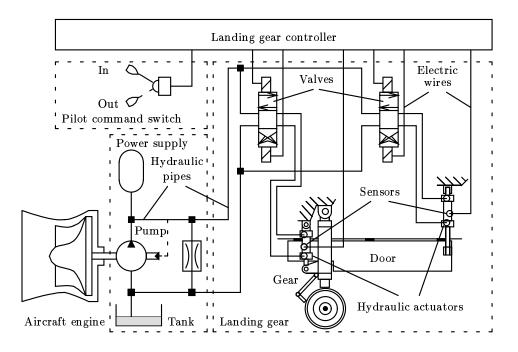

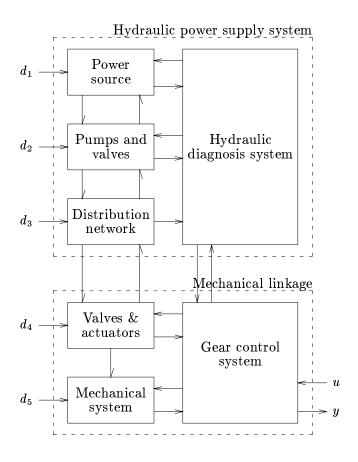

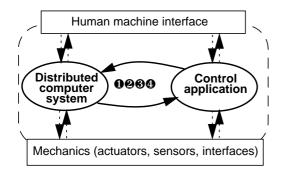

We describe a novel tool developed to support architectural design of distributed real-time control systems. The approach enables the co-simulation of functionality (from discrete-time control to logic) together with the controlled continuous-time processes and the behavior of the computer system. In particular, modelling and simulation of distributed computer control systems is supported allowing analysis of timing and control system robustness. An emphasised feature of the tool is its multidisciplinary and integrated approach that combines the views of control and computer engineering into one view at an appropriate level of abstraction. The use of the models and the tool is illustrated through examples and the usefulness of the approach for architectural design is discussed together with avenues for further work. The current models and the tool are designed with the modelling and analysis of fault-tolerant systems in mind. Improved support in this direction is the subject of ongoing work.

#### 1. Introduction

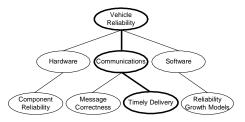

The mechatronics perspective provides a large number of opportunities to create improved machinery with the aid of software, electronics, sensors, actuators and control. Modern machinery, such as automobiles, trains and aircraft, are equipped with embedded distributed computer control systems, in which the software implemented functionality is steadily increasing. At the same time, a number of challenges face the developers of machinery in order to really be able to benefit from the technological advances:

- *Managing complexity* arising from the sheer amount of new functionality, as well as the non trivial dependencies between system functions and components.

- *Managing and exploiting multidisciplinarity* in order to achieve cost-efficient solutions and maintain

consistency (e.g. between goals, assumptions, design and implementation) during development.

• *Verification and validation of dependability requirements* with the challenge of developing mechatronic systems that are safer and more reliable than their mechanical counterparts.

Taking the current automotive systems as an example, the computer system is typically composed of a number of nodes connected via communication networks. With the introduction of new functions in vehicular systems it is inevitable that these will share resources in terms of sensors, actuators, communication links and computer nodes with the incentive of cost reduction. For example, in a brake-by wire system, the dimensioning of the brake actuators will need to consider not only the basic "by wire braking", but also braking demands from vehicle stability and cruise control. Functional coordination will consequently be an issue of increasing importance. The sharing of sensors will influence the choice of sensors, filtering and the information distribution. Computer system sharing influences resource management and timing. Perhaps most importantly, all types of sharing will have impact on the system dependability and maintainability.

The development approach of such future mechatronic systems, however, is still vague partly because the application area is young and partly since it requires the integrated cooperation of various disciplines from mechanical, control and computer engineering. A key element in addressing these challenges is to develop models, methods and tools to support, in particular, the so called *architectural design* stages.

#### 1.1. The road towards architectural design

Essential architectural design decisions include determining:

• The overall system structures, including functional, software and computer structures.

- The principles and means for error detection and handling, and at what level these should be implemented.

- The policies for resource scheduling, synchronisation, communication, and function/software triggering.

Establishing a system architecture requires considering conflicting requirements such as cost, flexibility, safety and reliability. One difficulty and typical characteristic is that while some of these properties, such as reliability and performance may be quantifiable, others are difficult or impossible to quantify, and in choosing an architecture, the balancing and resulting trade-offs become more or less subjective.

Architectural design requires the use of appropriate models that describe structural and behavioural properties [9], [4]. Models together with proper analysis tools provide the possibility to perform solution space exploration early in the development process, and prior to the point in time where physical hardware (mechanics and/or electronics) is available. Models also capture knowledge and form the basis for reuse. A model and architecture based approach is clearly highly motivated given the current state of practice in industrial development of embedded control systems where huge efforts and resources are spent on testing and debugging. From an industrial perspective, Hanselmann [8] points out the need for, and the current lack of, tools that allow early analysis and verification of distributed control systems.

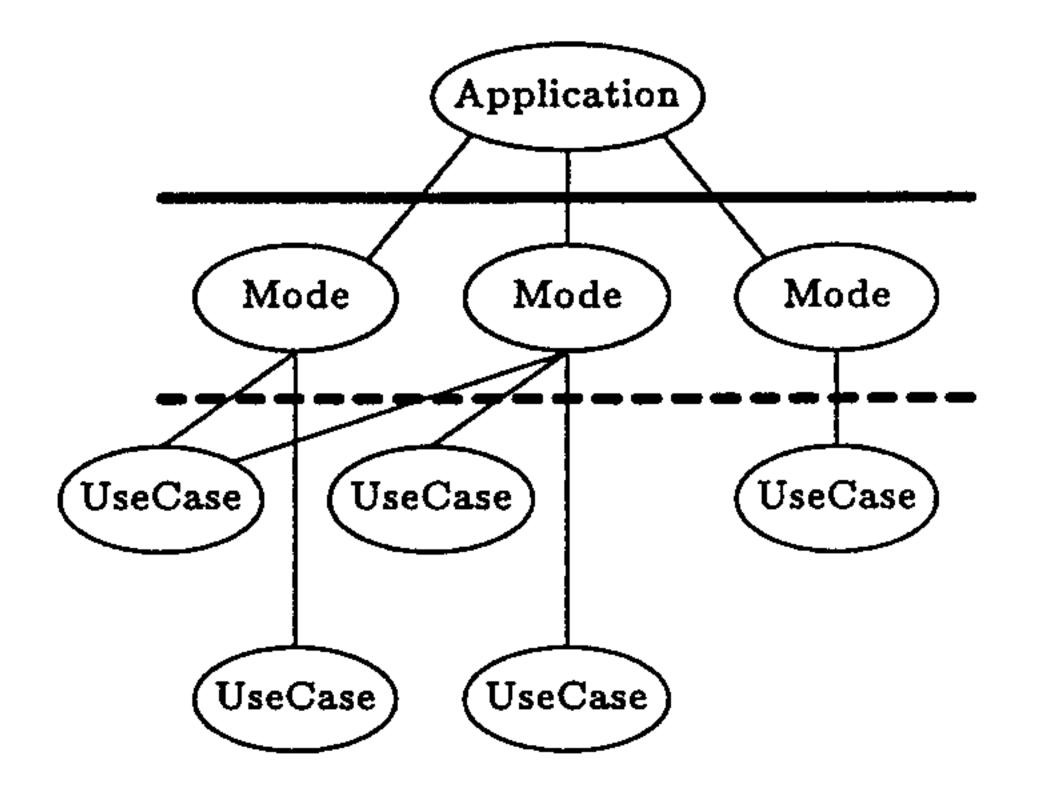

The next section describes the general approach taken in this project, followed by related work in section 3. Section 4 gives an overview of the model adopted in this approach. After some implementation details in section 5, our approach is illustrated in section 6 by walking through a simple example. Finally, this paper concludes with some future work proposals.

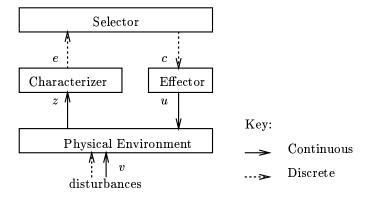

#### 2. Approach and focus

The suggested approach allows for the analysis of various architectural design decisions, and their impacts on control functionality, through a modelling and simulation tool. This analysis is intended to be carried out early in the development process and being useful for engineers from various disciplines. The co-simulation of the control system functionality together with implementation details of the chosen computer structure, allows the user to directly study the resulting system behaviour, and thereby gives the possibility to try out different architectures. In addition, the modelling process, spanning control design and computer system implementation, is important as such in that it promotes the interdisciplinary design. The tool simulation approach obviously needs to be complemented by other types of analyses and approaches, such as control analysis for performance and stability, and static timing analysis.

The work described in this paper in particular allows the modelling and simulation of:

- *Application software* encompassing different functionalities in a wide variety of styles (e.g. discrete-time, even-triggered, data-flow, state machines etc.).

- *System software* such as communication protocols where in principle the same modelling styles are used as for the application software. The concurrency model includes scheduling and thread interactions such as inter thread communication.

- *Distributed computer systems* including networks and computer system nodes (composed of processors with network and I/O interfaces). Global scheduling is supported including scheduling of processors, local and global communication, and other resources.

- *Mechanical systems* with sensors, actuators and mechanical system dynamics.

The work forms part of a larger research effort at the Mechatronics lab [14] where a common denominator is the development of a toolset supporting model based architectural design with different types of analysis. An essential requirement for the models and the toolset is the interdisciplinary design support encompassing system, control, computer and mechanical engineers. This will require a large set of models and analysis features including models encompassing discrete-time control, finite state machines, continuous time dynamics, software tasks and resource management. Our approach is to build upon and reuse existing models and tools where appropriate, and to add models and analysis features as required, as illustrated in this paper.

#### 3. Related Work

From a control system point of view, modelling and simulation of distributed system implementations has been used at least since the late 80s. The typical approach is to map all implementation related problems into control related effects such as time-varying feedback delays, sampling period jitter, data loss and permanent errors causing open loop drift (e.g. controller stuck at the maximum value) [12], [15], [22]. In [18] it was shown how special Simulink [10] blocks, can be developed to model these effects. Although this approach is suitable from a control design point of view it does not explicitly model the real-time computer implementation and thus lacks in supporting holistic architectural design.

Simulation tools such as the ones described in [16], [2] and [23] tackle various aspects of the design and analysis of

real-time applications. They are, however, limited in their use in the multidisciplinary approach suggested in this paper. The models used may be too abstract or domain specific to be understood by another discipline. Also, the tools' aim could be to analyse a particular aspect of the system such as a communication protocol or a specific operating system. In particular, little support exists for the co-simulation of a control application with the computer system. Exceptions to this are the tools described in [5] and [6], in which a control application can be simulated together with a task scheduler, and with potential extensions to include data sharing mechanisms. However, the usability aspects of this tool are weak from the mechatronics perspective since the control application needs to be implemented in code prior to simulation and changes to the system parameters are not straightforward.

There is relatively little work on interdisciplinary modelling. Exceptions in this regard include [21], [11] and [3]. The latter two describe work that deals with safety and reliability analysis in the context of computer control systems.

More detailed surveys of related work can be found in [13] and [20].

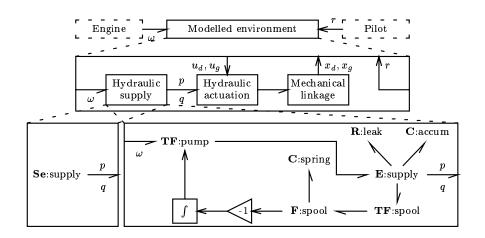

#### 4. The Model

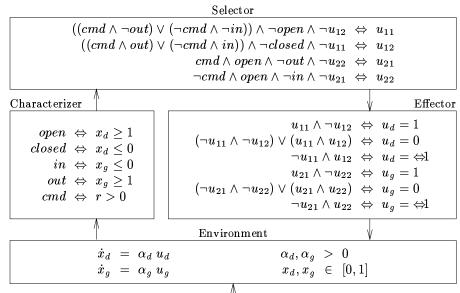

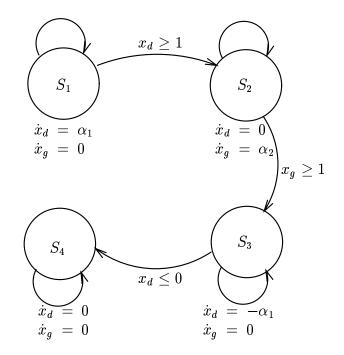

In order to achieve the goal of a multidisciplinary modelling environment, modelling aspects were borrowed from models in the various disciplines. In particular, three models are worth pointing out here. The AIDA modelling framework [13] provided insights into the control implementation requirements needed, the component models and their parameters. As a software engineering design methodology and model, the CODARTS method by Gomaa [7] highlighted the aspects of software that need to be included. Finally, the control engineering approach of using data flow diagrams was kept in the modelling of the internal task structure.

Inspiration is also drawn from an industrial case study where the task was to evaluate the fault-tolerant computer control system of the SMART satellite, to be launched by the European Space Agency in 2002. The aim of the evaluation was to analyse the high level redundancy protocols being introduced in the system, and their behavior when implemented using the Controller Area Network (CAN). The work entailed modelling the distributed faulttolerant computer system and simulating its behaviour during stipulated failure modes such as loss of communication, node loss, and various CAN controller failures. The modelling, tool development and evaluation efforts are further described in [19]. The models described below maintain a good balance between three factors that were considered important. First, a good representative model is needed to reflect real entities in the system and which is not too mathematically abstract. At the same time, an executable model needs to be well defined and unambiguous. Finally, the model should contain a minimal number of different components with a simple and generic interface in order to simplify the development and use of the tool.

#### 4.1. System Topology Model

At the top level, the hardware topology of the whole system is modelled. This hardware structure consists of three types of components: The surrounding environment, communication links, and the computer nodes. The node model will be described in more detail in section 4.2.

**Environment.** It is necessary to include the environment into the model in order to define its connection to the embedded computer system. With the types of applications considered here, the most apparent entity that needs to be modelled is the mechanical dynamics of the system including sensors and actuators. For this, well-established mathematical models exist. These models will not be discussed any further and the reader can refer to a wide range of dynamics textbooks for details. It is however necessary that the chosen environment model is integrable with the rest of the hardware model, meaning that it should be possible to actuate and sense appropriate parameters of the mechanics.

A computer node connects to the system environment at various points. This connection is performed via Hardware Units (see "Hardware Units" in Section 4.2) such as pulse width modulators (PWM), analogue to digital converters (ADC), and digital to analogue converters (DAC) that reside in the node.

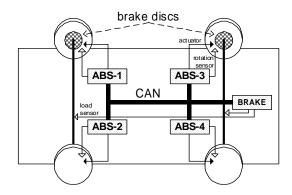

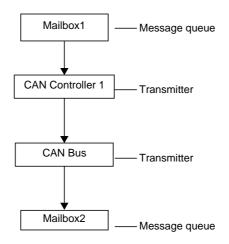

**Communication Link.** A communication link provides data exchange facilities between computer nodes. It defines the protocols that handle the messages being sent between connected nodes. A communication link indirectly interacts with each connected node through *communication controllers* that reside in the node. The communication link performs the scheduling of messages requested from connected controllers, while the controller internally schedules its own messages. Such a setup allows for a representation of a multitude of node and link models to be connected, as well as allowing for a node to connect to one or more links, and vice versa.

As an example, consider the implementation of the CAN bus. Requests to send messages on the bus are received by the bus from the controllers. These requests are only serviced if the bus is idle, and ongoing transmissions are not disturbed. Once the bus is idle, controllers arbitrate between each other to gain access to the bus according to the CAN protocol. The message transmission time depends on the bus bit rate and the message size including any protocol overheads. Note that the arbitration within a CAN controller is performed independently at the node level, and that this local scheduling is not part of the CAN protocol itself.

#### 4.2. Node model

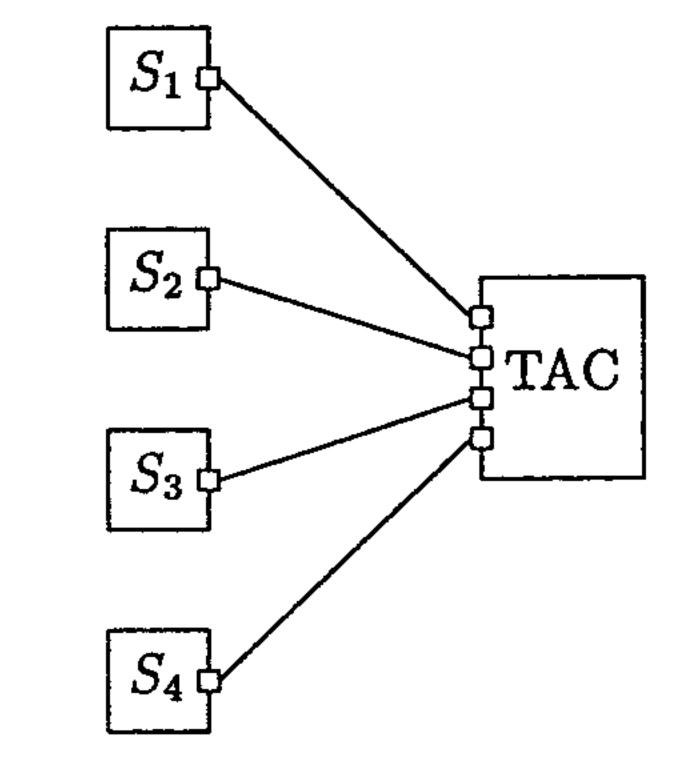

A node consists of the following types of components:

- One or more tasks from which the system software is built. The task model is described in section 4.3.

- A task scheduler.

- Zero or more operating system Service Providers (SP) such as inter-task communication, task synchronisation and semaphores.

- Zero or more hardware units such as communication controllers, timers, ADCs and DACs

- A processor.

The application functionality to be developed by the user is composed of application tasks, with services provided by the other components comprising the operating system. Software layers, which interface the application software to the system hardware and operating system, can be easily modelled and designed with this approach. For example, system tasks, belonging to the operating system, can be developed to implement software drivers or high level network protocols.

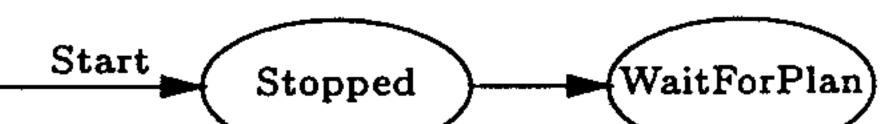

**Scheduler.** A single task scheduler exists for each node in the system. The scheduler's role is to, when triggered, simply choose and activate a single task that is to run on the node processor at that time. The scheduler may be triggered by any of the service providers installed on that node, or by a timer reaching certain predefined points in time. A *task list* component also exists which holds certain information on each task such as its ID, current status, priority and any user-specific parameters. The scheduler only needs to interface to the task list in its decision making, and different scheduler models require different information about the tasks and hence, the task list model should be consistent with that of the scheduler.

This model allows for the modelling of a wide range of schedulers such as event/time triggered, static/dynamic, and off-line/on-line schedulers. Developing a new scheduler requires the implementation of the function that decides on the next running task, as well as the design of the data structures needed for each task in the task list. Using a particular scheduler simply requires the inclusion of the scheduler and its accompanying task list into the node, and any off-line customisation is done by the user through the task list.

As an illustrating example, consider the design of a fixed priority preemptive scheduler. The task list stores, for each task, the user specified static priority as well as its current status. A task status can be one of *ready*, *running* or *blocked*. The scheduler in this case is triggered every time a task changes its status in order to evaluate if a more legitimate ready task needs to run on the processor. A scheduler triggering may be caused by, for example, an interrupt or a service provider.

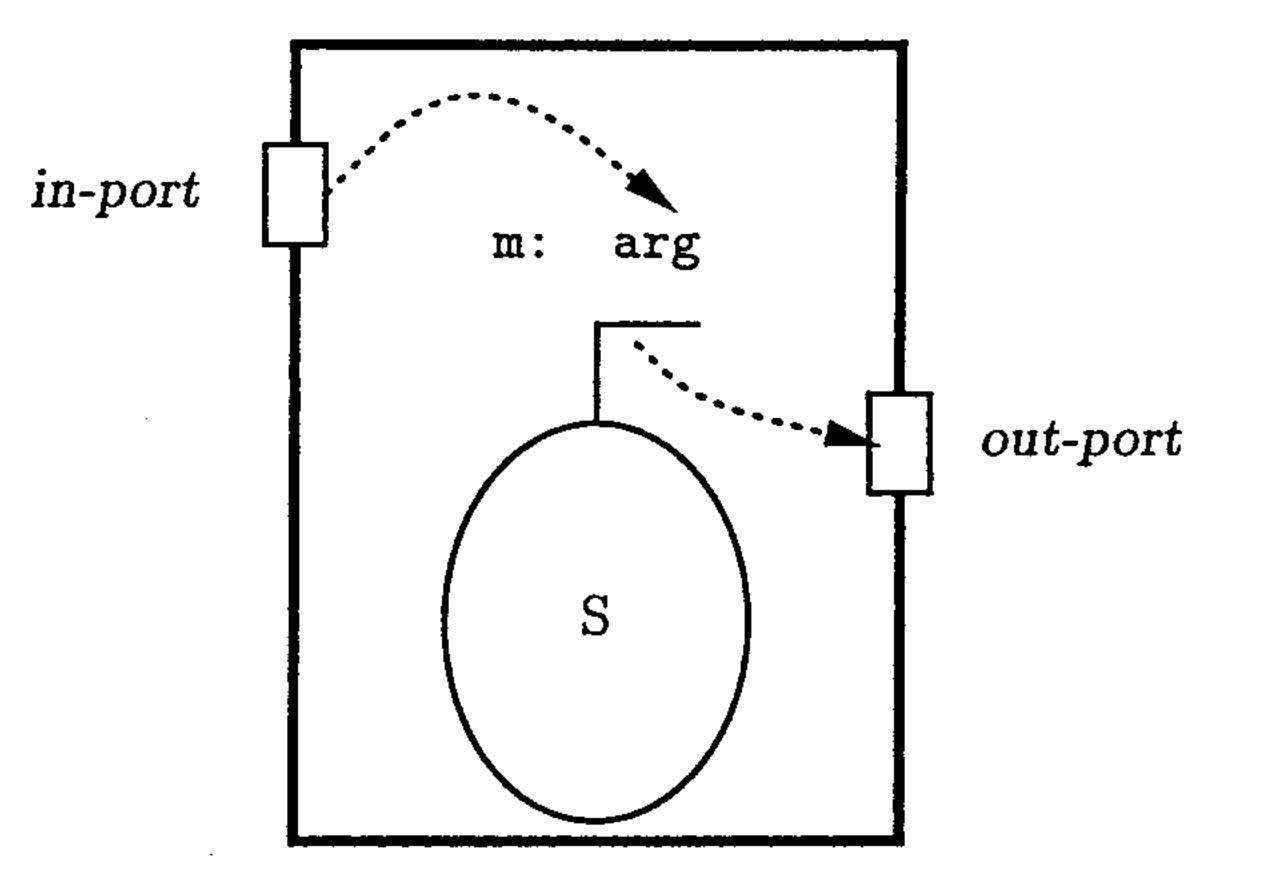

**Service Provider.** Examples of service providers are intertask communication and task synchronisation. Although they vary in their functionality, these components have very similar features and interactions to the rest of the system. Essentially, a *service provider* (SP) responds to a *service request* from a task to perform certain activities. This activity may cause the calling task (or any other task, in general) to change status due to the internal state of the SP.

The mechanism of making requests by a task and the response to these requests is fixed across all services. What varies is the interpretation of the requests and the way they are handled. Hence, developing new services simply requires the definition of the internal states, and the functionality to handle the various types of possible requests. All SPs have access to the task list and are able to trigger the processor scheduler.

As an example, consider an inter-task communication service implemented as a first-in/first-out, block-on-full service. When a task requests to send a message, it simply sends the data to the specific SP. Normally, the SP places the data in the FIFO buffer. However, if the buffer is full, the SP changes the task status to blocked, and triggers the scheduler. When the buffer is available again, the SP changes the task status to ready and triggers the scheduler.

**Hardware Unit.** Hardware units may be fully embedded in the computer node (such as a floating point processor) and hence only interfacing with the processor, or they could lie on the border (such as an ADC) and provide an interface between the processor and the surrounding environment.

From the task perspective, the interface to a hardware unit is similar to that of a service provider in that a request is made for a service which the unit provides. Hence, it is important to match the requests to the correct service. However, a hardware unit differs from a service provider in that it has no direct access to the internal data structures of the OS such as the scheduler or task list. Instead, the unit may cause processor interrupts that tasks in the system need to handle appropriately. This model naturally facilitates the masking of these units by developing unit drivers (consisting of system tasks) that encapsulate the hardware units and handle the generated interrupts.

As a simple example, consider a hardware unit implementing a CAN communication controller. A task requesting to send a message over CAN makes a request for service by directly accessing the hardware registers. The unit in turn communicates with the associated CAN communication link, and upon receiving a message from the link, produces a hardware interrupt (if so configured). The CAN controller performs the local scheduling of simultaneous transmission requests, e.g. FIFO or priority based.

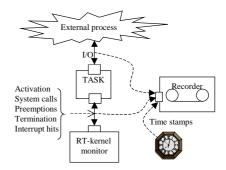

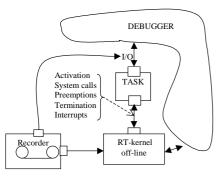

#### 4.3. The task model

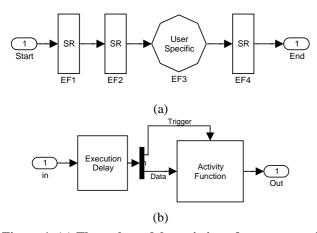

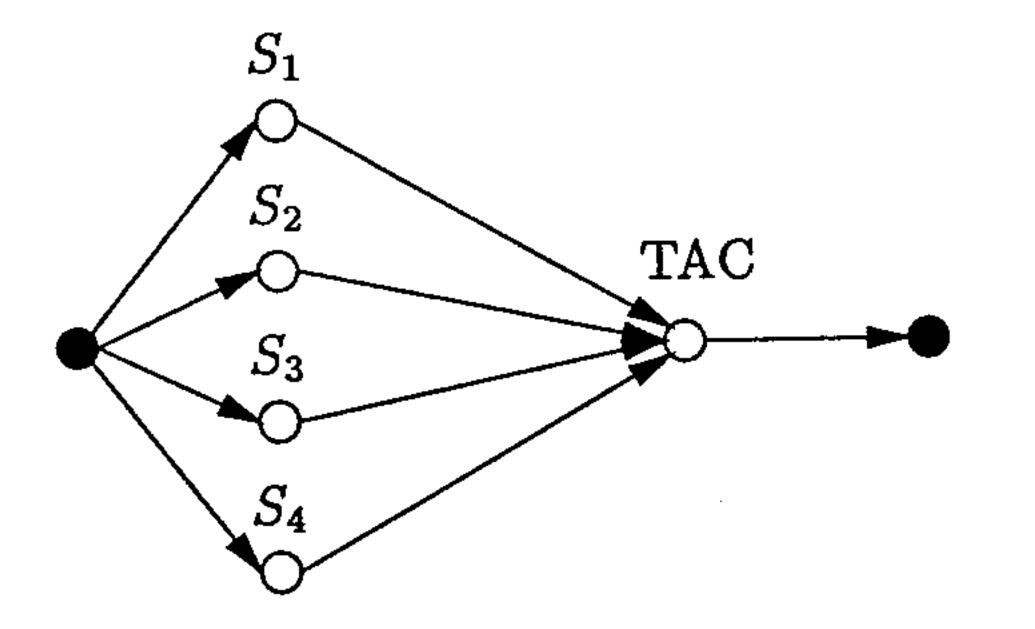

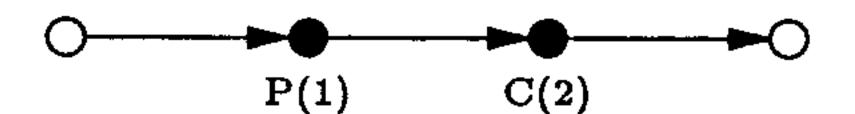

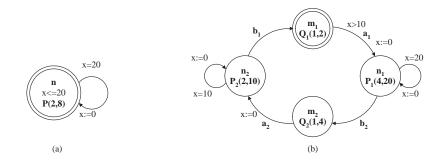

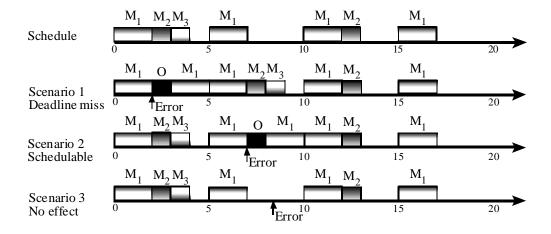

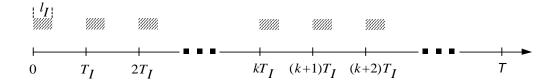

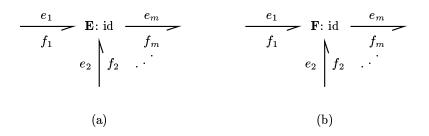

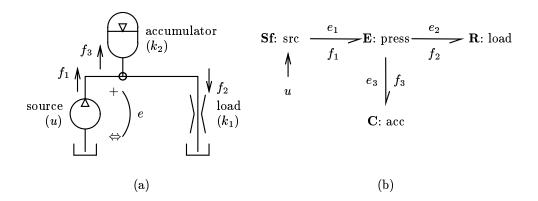

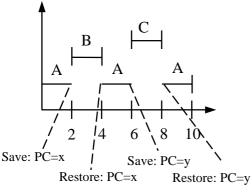

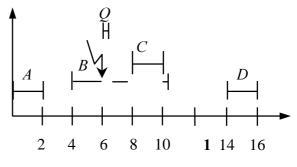

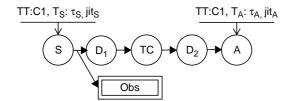

A task is modelled as a single sequence of *elementary functions* (EF). Each EF is assumed to take a specified nonzero amount of time to execute. We can draw a simple task as shown in Figure 1a, illustrating the precedence relationship between the elementary functions. The EF can be either user-specific (octagonal block representation) or an operating system service request (rectangular block).

### Figure 1. (a) The task model consisting of a sequence of elementary functions (EF). (b) The internal model of an EF.

When first triggered, the task is made ready to run on the processor. During its lifetime, and depending on the system activities and the scheduler being used, a task runs on the processor at different time slots. The directed link between two EFs within a task indicates passing control from the source to the destination EF, triggering the destination EF to begin its execution. The currently activated EF terminates once the task executes for a time period that is equivalent to the EF execution time, since the EF was first activated. When the control is passed to the last block, the task is terminated.

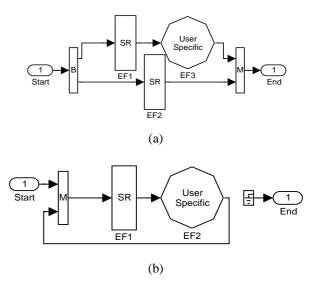

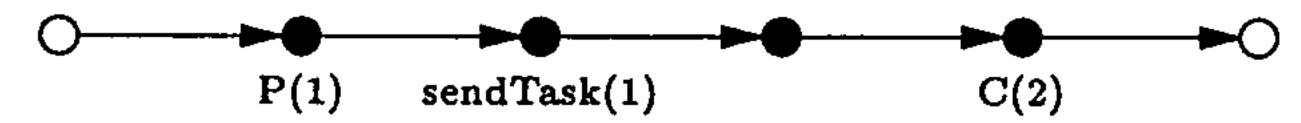

This simple model can be extended in order to provide looping and branching of the elementary functions, as shown in Figure 2. Once triggered, the Branch block (B) produces an output trigger in one, and only one of its outputs, based on internal logic. The Merge block (M) produces a trigger on the output as soon as any of its inputs is triggered. These mechanisms do not consume any processor time, and are only intended to be used for high level modes of operations of the application.

Tasks may be initially triggered as soon as the node is booted, or they may be configured to be triggered by an interrupt. The first is typical for many application tasks, while the latter can be used to model system interrupt handlers. It is also necessary to have at least a single task (the system idle task) in the system that is initiated during boot time, and that may never terminate.

Figure 2. Examples of more complex task structures such as (a) branching or (b) looping.

**Elementary Function (EF).** The internal model of an EF is shown in Figure 1b. The input to an EF (either user-specific or an operating system service request) consists of the elementary function trigger and its data. When an EF is first triggered, the input data is captured and when its specified execution time elapses, an output trigger is produced together with output data. By definition, an elementary function may be preempted at any instance in its execution. Non-preemptive EFs can be implemented as a subset of normal EFs, by implicitly surrounding each elementary function with service requests that disable and enable preemption.

#### 4.4. Model attributes

Table 1 lists the explicit attributes that the user needs to specify for each of the components in the model. In addition, components contain implicit properties that can be automatically derived from their context. For example, a task implicitly identifies the list of elementary functions that are contained within it. Also, each component contains a unique identifier that distinguishes it from other components.

| Component                          | Attributes                                         |

|------------------------------------|----------------------------------------------------|

| Communication link                 | Link Speed<br>Communication Protocol               |

| Scheduler                          | Scheduling Algorithm                               |

| Service Provider/<br>Hardware Unit | Service Response Policies<br>Internal Buffer Sizes |

| Elementary Function                | Execution Time                                     |

Table 1. Explicit component attributes.

#### 4.5. Software structure

As well as being executable, the models described above are representative enough that the collection of task models from each of the nodes in the system can serve as a basis for a detailed software model, which could be translated to a more traditional and familiar form, if desired. Sufficient level of detail is available to generate pseudo-code for each task in the system, and configuration information indicating the services needed for each node.

#### 5. Simulator Overview

In this section, we will give a brief outline of the simulator implementation of the above models. More detailed description requires extensive explanations of various Matlab/Simulink aspects and is the subject of a technical report to be produced in the near future. The Matlab/Simulink toolbox [10] has been chosen to implement the simulator for the following reasons:

- Working in the control engineer environment allows the control engineer to specify, validate and interact with the computer engineer in a familiar environment that reduces the chances of ambiguity and confusion.

- A rich API is available for the extension of the tool in a variety of languages such as C and Java. Combined with the broad range of existing blocks, the tool development is simplified, particularly for monitoring and testing.

- Simulink allows for the integration of custom code into its models. Hence, it is possible to model the control application together with any encapsulating software. In addition, Simulink supports hierarchical models.

- Simulink supports modelling and simulation of hybrid systems.

- Many commercial development tools such as rapid prototyping tools, working with Simulink, can give a well integrated working environment.

On the other hand, there is a strong gap between the Simulink modelling level and the real-time system implementation, further motivating this work.

The handling of hybrid systems required the simulator to have an event-triggered architecture, where all the activities in the system are event-triggered, and the Simulink triggering capabilities are used extensively. Note that this still allows for the modelling of purely time-triggered architectures, where time is viewed as an event. A combination of C-coded S-functions and Simulink blocks were used in the implementation.

Each of the model components discussed in section 4, is actually represented in the simulator as a Simulink block. The drag-and-drop approach of blocks from libraries is used to build the models. Blocks are then customised through a graphical user interface. Also, there are no restrictions on the types of standard Simulink blocks that can be used with the simulator models, except for those imposed by Simulink itself. This ensures a well integrated environment with Simulink and the user does not need to learn a new tool.

As can be seen from the definitions in section 4, there is extensive data exchange between the components. Taking the traditional Simulink approach of connecting blocks to exchange data is not favourable since this will certainly complicate the model for the simplest cases. Even worse, confusion will occur between data exchange of the application itself and that needed for the implementation of the underlying components. The approach taken in the simulator is to hide all data exchanges that do not form part of the representation model of the system. For example, although data exchange is necessary between a scheduler and each of the tasks on its processor, these links are not explicit in the model presentation since they do not contribute to the understanding of the model. The user need not be concerned with these hidden links since each component automatically reconfigures itself based on the presence of other blocks in the system. Also, the interface between these types of components within a node is well defined and fixed, allowing for the independent development of subtypes and variations in the internals of each of the components.

The simulator permits the user to monitor any variable in the system, as illustrated by the examples in section 6. Parameters that may be of interest for timing analysis include a task's status, the times when particular events or activities within a task occur, or the time when a service request is serviced.

#### 6. Illustrative Examples

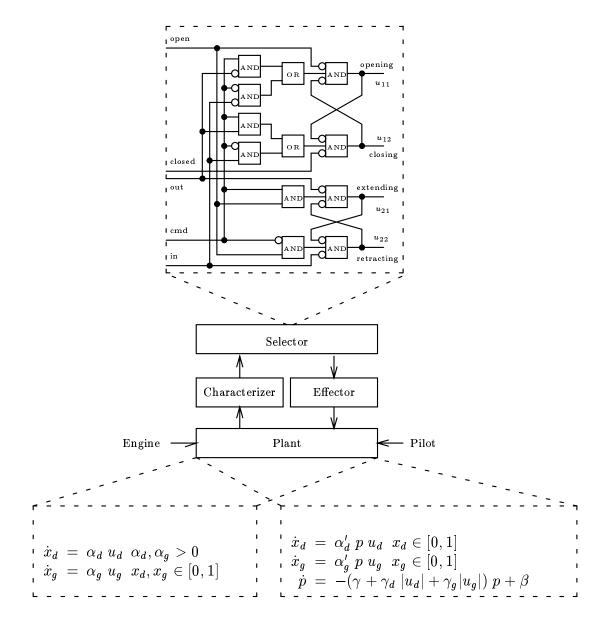

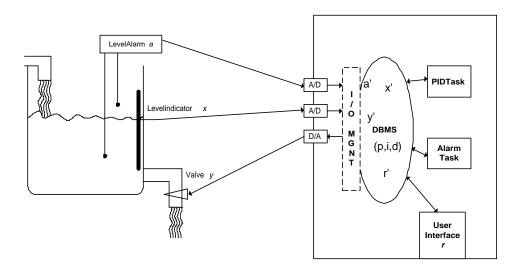

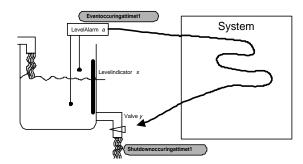

The aim of this simple example is to demonstrate how the tool can be used in architectural design for the evaluation of the computer implementation effects on the control performance. We will proceed from a pure functional design, to a single node and a distributed system implementation. In addition, the usability aspects of the tool are illustrated.

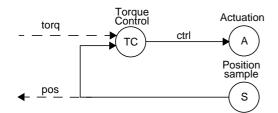

#### 6.1. Controller Design

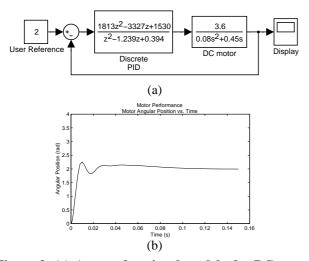

Consider the problem of controlling the angular position of a DC motor in order to reach a set point specified by the user. The control algorithm is to be implemented on a computer system. After modelling the mechanics of the motor, the control engineer uses established techniques in designing a discrete controller that produces acceptable performance. A Simulink model of the resulting system is represented in Figure 3a.

Figure 3. (a) A pure functional model of a DC-motor controller together with a model of the motor dynamics. (b) Closed loop performance of the system in Figure 3a for a step response.

In this example, a continuous time PID controller was developed and then translated into a corresponding discretetime controller. A sampling period of 2ms was chosen according to standard rules of thumb [24]. The angular position of the motor and the user reference value are measured by the controller. The controller outputs and controls the motor voltage. This information becomes the software specification to be implemented. At this stage of development, important requirements such as controller jitter and delays are often overlooked, since they are dependant on implementation details and their values can only be deduced once the system is implemented. As shown in [5] and [22], these parameters are critical to ensure a certain controller performance. One approach to determine these parameters is to iterate between the control design and the software implementation until satisfactory results are achieved. Another cheaper alternative is to model and evaluate the computer implementation effects early in the design stage, and to try to take appropriate design measures before the implementation is carried out.

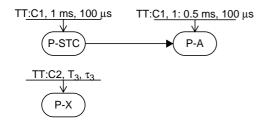

#### 6.2. A Single Node architecture

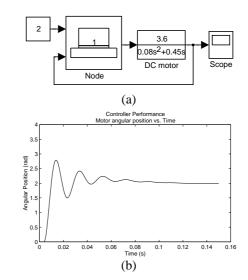

Assume that it has been decided that the whole controller application should be implemented on a single computer node. Having identified what needs to be measured from the system environment, it is deduced that two ADCs and one DAC are needed. A complete model of our hardware structure is given in Figure 4a.

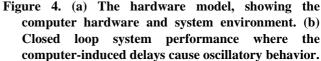

The node internal structure is shown in Figure 5a. The application is to be divided into two tasks. The first, called the Sensor task, performs the sampling of the sensor values, while the second, called the Controller task, executes the control algorithm. Data sharing between the two tasks is to be done via a FIFO, block-on-empty, inter-task communication buffer (FIFO\_Buffer). The tasks' internal

structures are shown in Figure 5b. The sensor task is triggered periodically (WaitTrigger) by a system timer with a period of 2 milliseconds; the trigger is produced by an interrupt handler task (IH\_Task) and communicated to the sensor task via a buffer (IH\_Trigger). The controller task is triggered by the arrival of messages (the sampled sensor values) from the sensor task.

Figure 5. (a) Internal node configuration. (b) Internal task structure for the Sensor and Controller tasks.

To build this model, the developer simply drags and drops the blocks from the Simulink library. The parameters of each block are then customised through a GUI. Partitioning is performed by copying the blocks from the original control model (e.g. "discrete PID" block in Figure 3a.) into the appropriate EF (e.g. "Controller EF" in Figure 5b). The execution time of each EF is then specified. Having chosen a fixed priority preemptive scheduler for this node, the user can specify the priority of each of the application tasks in the system. The task list is designed such that the priority of system tasks are automatically generated by the task list component and may not be modified by the user. Once the model is built, a simulation is performed and output devices such as scopes can be placed in various parts of the system to monitor any data required. Figure 4b shows the motor angular position. Note the difference between this controller performance (such as overshoot, rise time and settling time) and that achieved by the pure functional model in Figure 3b.

By instrumenting the model, various jitter and delay parameters were measured. For example, the motor actuation occurred 1.4ms after the sensor reading. This delay caused the change in the controller performance detected in Figure 4.

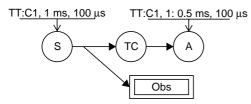

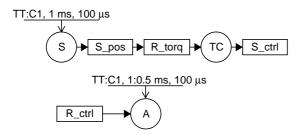

#### 6.3. A distributed architecture

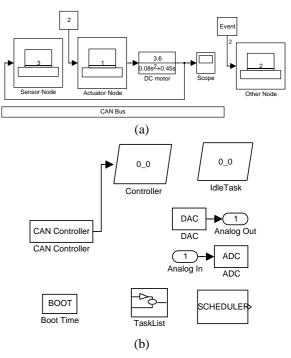

Now, assume that it is required to distribute this control application over two computer nodes. One node performs the sensor sampling, while the other node performs the motor actuation. CAN is chosen as the communication protocol between the nodes. Hence, a CAN bus is placed in the hardware model, with a CAN controller in each of the computer nodes. This architecture is shown in Figure 6a where the "Other Node" is added to introduce interference and blocking to the CAN communication.

The internal node and task structures are essentially similar to the previous example with the difference that the Sensor and Controller tasks are placed in the Sensor and Actuator nodes respectively. Also, the communication of the sensor samples is now performed over a communication link. Figure 6b shows the internal node structure for the "Actuator Node". The Controller task is triggered by the CAN Controller block upon receiving a message (the sensor value) from the CAN bus. In this example, the CAN bus bit rate is configured to 100kbit/s, and the sensor value is sent on the bus with an ID of three and a size of three bytes. For each CAN frame, the worst-case bit stuffing and frame overhead are assumed [17].

Figure 7. Closed loop performance for the (a) distributed architecture (b) distributed architecture, with interference at time = 25 ms.

This architecture gives the controller performance shown in Figure 7a. As expected, this is worse than that of the single node architecture since the transmission time of messages over a bus is longer than inter-task communication within a single node.

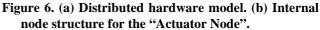

#### Studying the effects of interference and blocking.

Assuming the presence of other functions in the system, it may be desired to study how these affect our control system. Here, we assume that another application resides on a third node in the system and it periodically sends low priority messages (ID = 4) on the CAN bus as shown in Figure 6a. Also, at time = 25 ms, the node sends a single high priority message, (ID = 2) eight bytes in size, on the bus. How does this affect the controller application? By incorporating the third node in our model and running a simulation, the new controller performance can be investigated (Figure 7b). The arrival times of each message in the CAN controllers is shown in Figure 8.

Here, we see that the controller performance has degraded even further, with a transient glitch, due to the delays in communicating between the two nodes, induced by the new function. Such information can be used by the system designer for example to produce limiting requirements on the communication bandwidth of other functions in the system, and/or by modifying the control system to be more robust towards (varying) time-delays.

**Further Evaluation.** Early in the design stages, the developer may wish to evaluate the effects on the application of varying certain parameters such as the task scheduler, inter-task communication mechanisms, or the communication protocols used. The tool allows the simple exchange of such parameters by simply replacing a particular component with another and reconfiguring it appropriately, with minimal effort from the user.

#### 7. Future Work and Conclusion

This paper has described the current status of the models and toolset being developed at the Mechatronics Lab, as part of the AIDA project [1]. The analysis of computer induced effects (due to design faults such as timing problems and computer hardware faults) on the system behaviour, constitutes a kind of failure mode and effects analysis. We expect the simulation tool to be especially useful for evaluating different error detection as well as error handling techniques, spanning the computer and control system levels. As mentioned earlier, this work is to be extended in various directions in the future. Most importantly, it is desired to validate and evaluate this work through further industrial case studies, such as the evaluation of architectures for x-by-wire systems in other related projects at the Mechatronics lab. Currently, no emphasis has been placed on simulation efficiency; this may require work in the future.

Parallel to the work described here, an analysis tool, aiming at the timing analysis of distributed control systems, is also under development at the lab. In the future, the two tools are to be integrated, providing two complementary approaches for system analysis. This may necessitate the extension of the current models in order to overcome any unforeseen shortcomings in the models.

Certain tool implementation limitations also need to be overcome. For example, in the current implementation, the scheduler preemption overhead is not an explicit parameter of the scheduler and need to be specified for each task in the system. From the usability perspective, it will be desired to expand the current libraries (for example, with a collection of communication protocols) and extend the tool to support features such as redundancy mechanisms and clock synchronisation. Also, it is desired to further the development of hardware entity models, such as simple processors and smart sensors, allowing the modelling of functionality implemented directly in hardware.

#### 8. Acknowledgement

This work is partially funded by the national Swedish Real-Time Systems research initiative ARTES (www.artes.uu.se), supported by the Swedish Foundation for Strategic Research. The authors are also grateful for the valuable suggestions and reviews of the RTC group members (Ola Redell, Martin Sanfridson and DeJiu Chen) during the work described in this paper.

#### 9. References

[1] http://www.md.kth.se/~ola/aida/index.html

[2] Audsley N., STRESS: A Simulator for Hard Real-Time Systems, RTRG 106, Dept. of Computer Science, University of York (1991).

[3] Bass, J.M., Brown, A.R., Hajji, M.S., Marriott, D.G., Croll, P.R.; Fleming, P.J, Automating the development of distributed control software, *IEEE Parallel & Distributed Technology: Systems & Applications Conference*, Winter 1994, pp 9-19.

[4] Bass, L. and Kazman, R., *Architecture-Based Development*, Technical Report, Carnegie Mellon University, CMU/SEI-99-TR-007, ESC-TR-99-007.